ΤΜΗΜΑ ΜΗΧΑΝΙΚΩΝ Η/Υ ΚΑΙ ΠΛΗΡΟΦΟΡΙΚΗΣ

ΠΑΝΕΠΙΣΤΗΜΙΟ ΠΑΤΡΩΝ

# <u>Οδηγός Μελέτης &</u> <u>Εκπόνησης Εργαστηρίου</u> <u>Ηλεκτρονικής ΙΙ</u>

# Δρ. Χ. Μιχαήλ –Δρ. Φ. Γκιουλέκας

<u>Πάτρα, 2010</u>

#### 1. Γενικές Πληροφορίες

Το εργαστήριο Ηλεκτρονικής ΙΙ, είναι μάθημα του τετάρτου εξαμήνου και διεξάγεται στον εργαστηριακό χώρο απέναντι από την γραμματεία της σχολής, δηλαδή στον ίδιο χώρο που διεξάγονταν και το εργαστήριο της Ηλεκτρονικής Ι.

Το εργαστήριο διεξάγεται σε ομάδες των δύο ατόμων, και κάθε ομάδα θα εκπονήσει συνολικά πέντε εργαστηριακές ασκήσεις. Κάθε ομάδα θα προσέρχεται για εκπόνηση άσκησης, κάθε δεύτερη εβδομάδα σύμφωνα με το πρόγραμμα που έχει ανακοινωθεί. Για το ακαδημαϊκό έτος 2009-2010, τα εργαστήρια θα αρχίσουν από την Δευτέρα 1<sup>η</sup> Μαρτίου.

Είναι προφανές ότι για να συμμετάσχει κάποιος με αξιώσεις στην διεξαγωγή του εργαστηρίου Ηλεκτρονικής ΙΙ, θα πρέπει να έχει συμμετάσχει με σχετική επιτυχία στην διεξαγωγή του εργαστηρίου Ηλεκτρονικής Ι, ώστε να γνωρίζει τον τρόπο σύνδεσης των στοιχείων, λειτουργία των γεννητριών και του παλμογράφου καθώς και την εν γένει λογική του εργαστηριακού εξοπλισμού. Σε κάθε περίπτωση όποιος δεν γνωρίζει τα παραπάνω, θα πρέπει να καταβάλει σημαντικό κόπο, πριν την αρχή του εργαστηρίου, ώστε να διαβάσει τα αντίστοιχα εγχειρίδια χρήσης και να κατατοπιστεί κατάλληλα. Ειδάλλως δεν θα είναι εφικτό για αυτόν να διενεργήσει της εργαστηριακές ασκήσεις.

#### 2. Προεργασία Εργαστηριακών Ασκήσεων

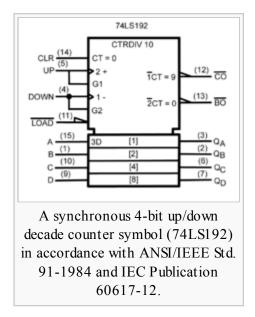

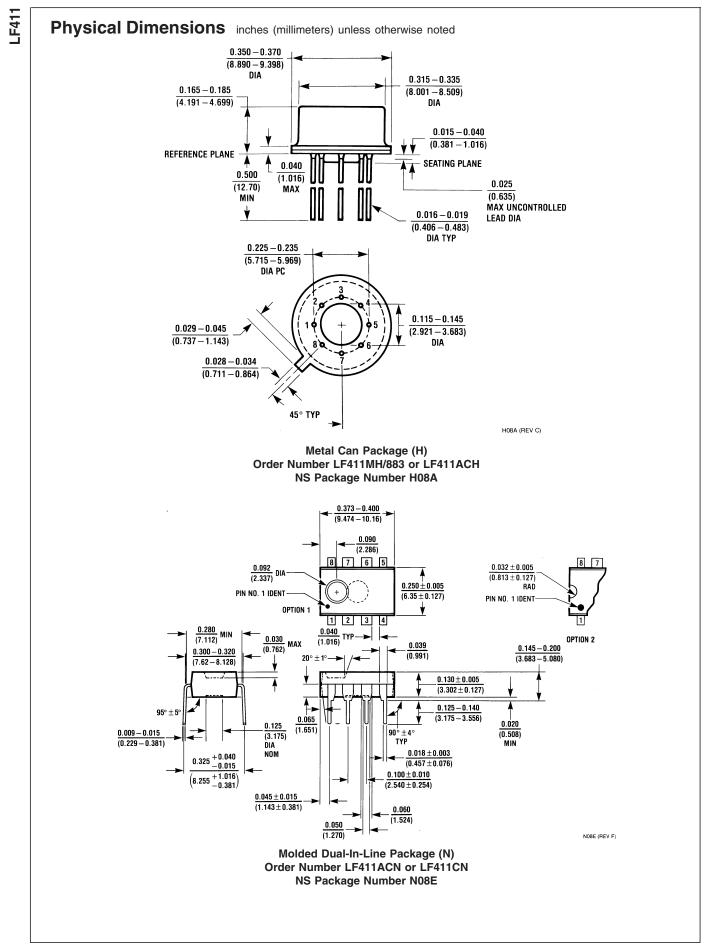

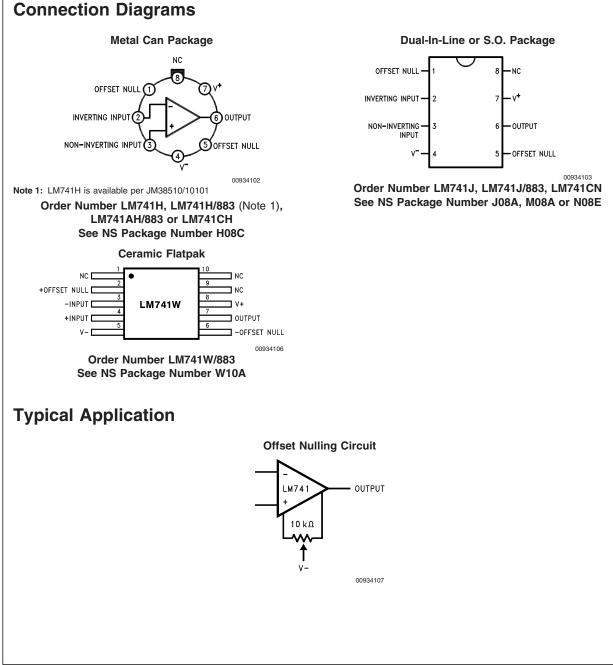

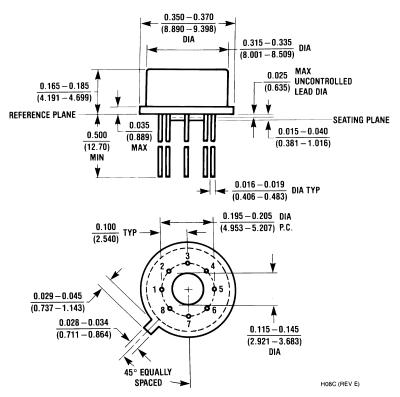

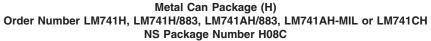

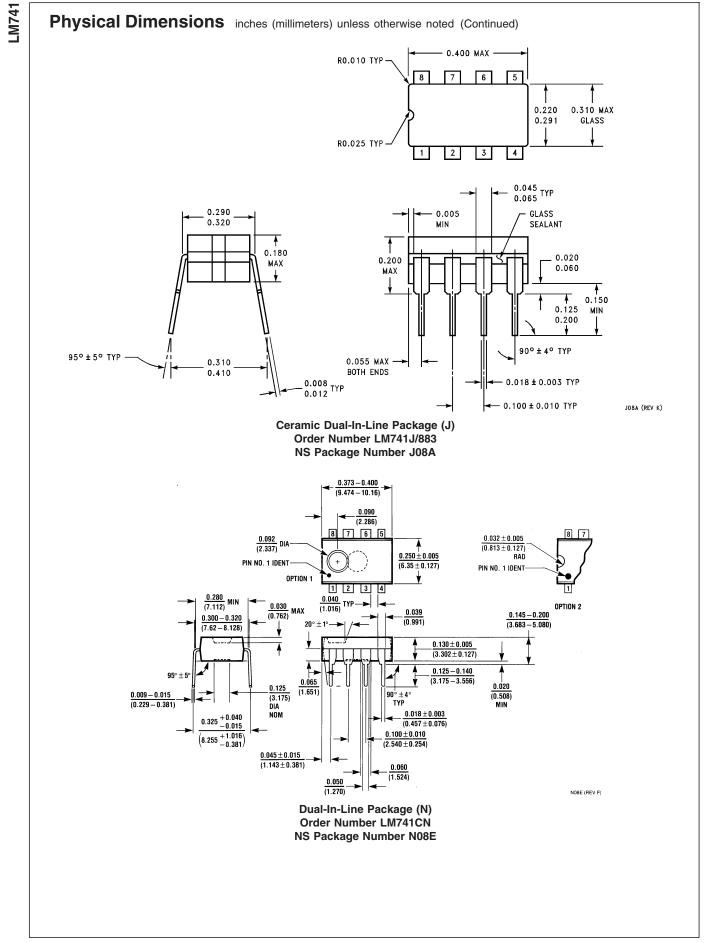

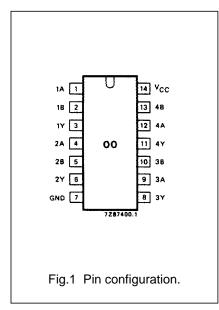

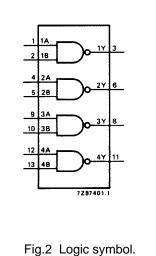

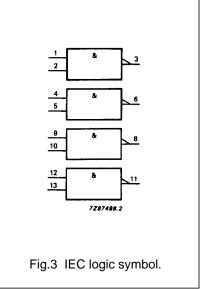

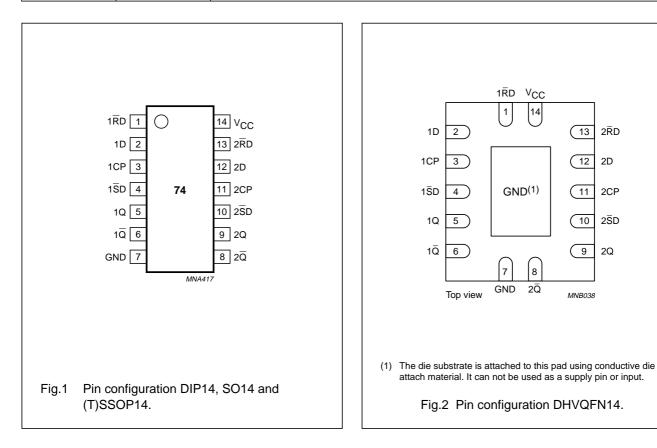

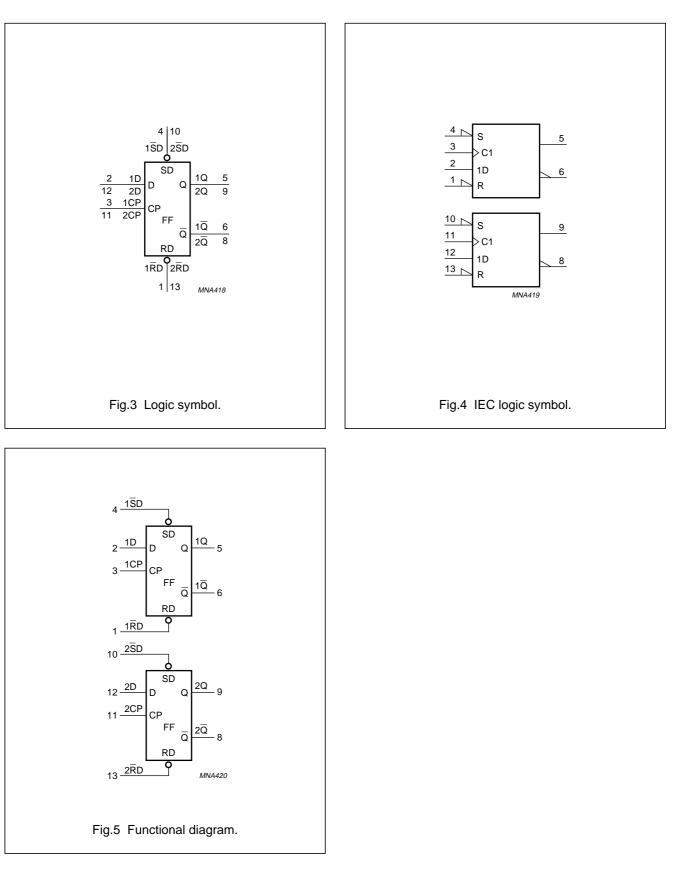

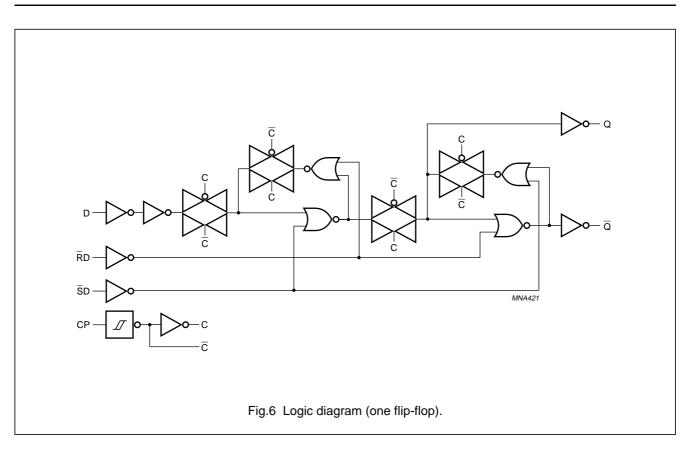

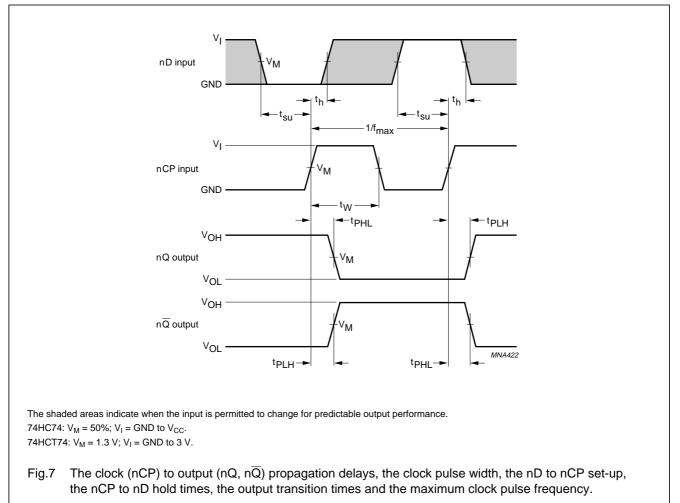

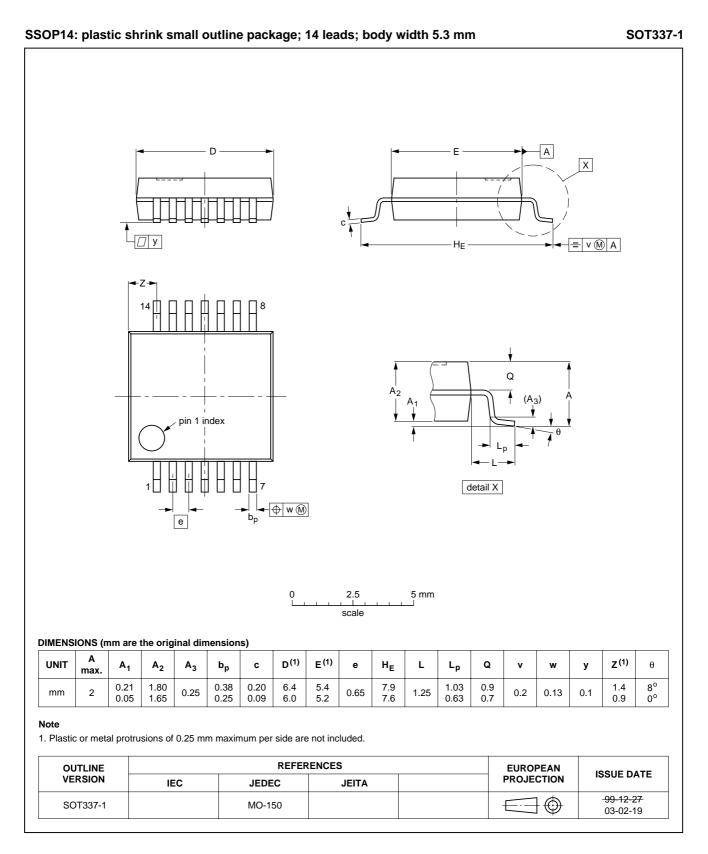

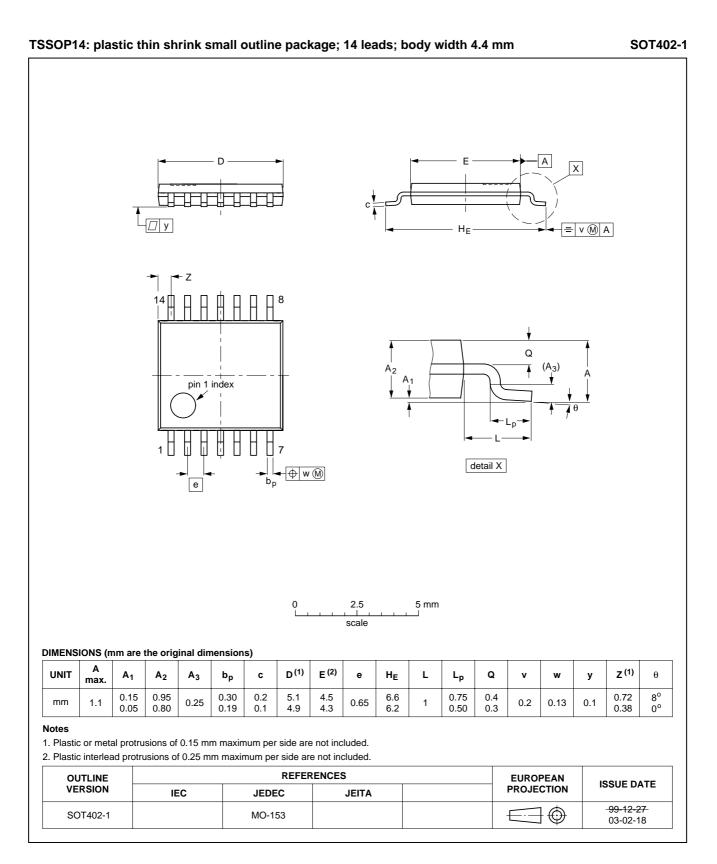

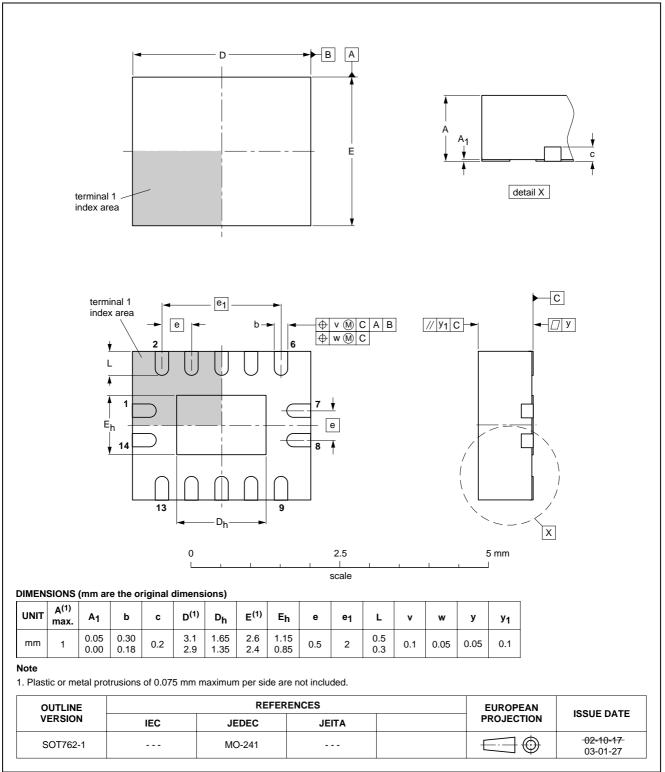

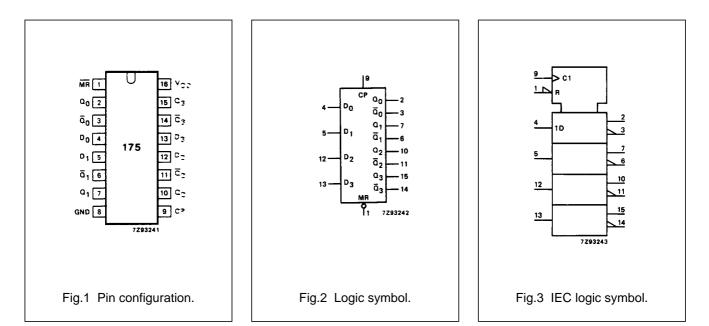

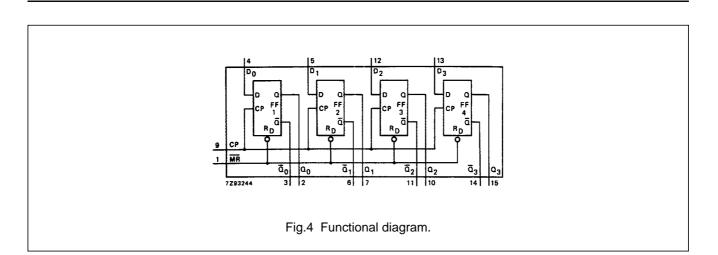

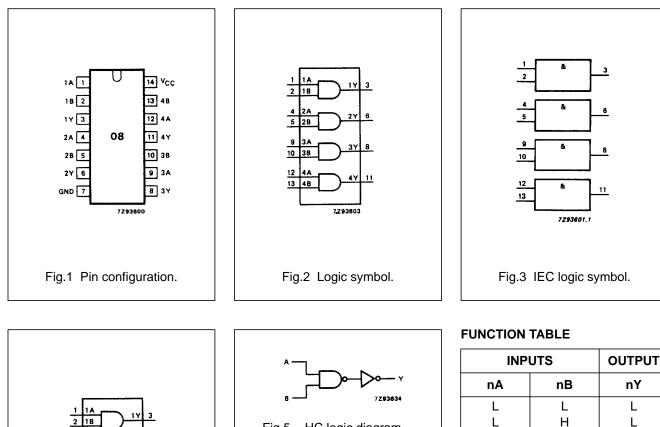

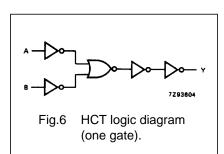

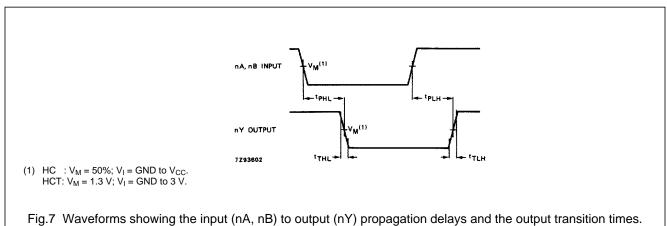

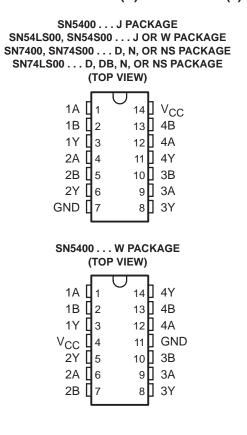

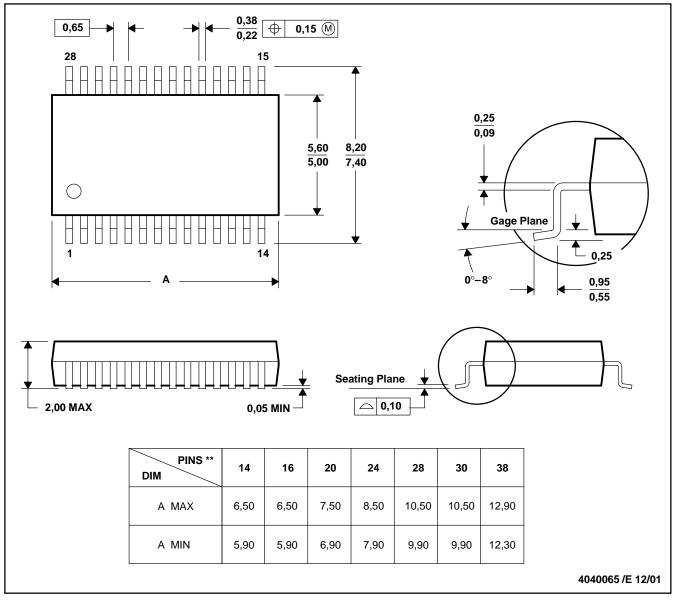

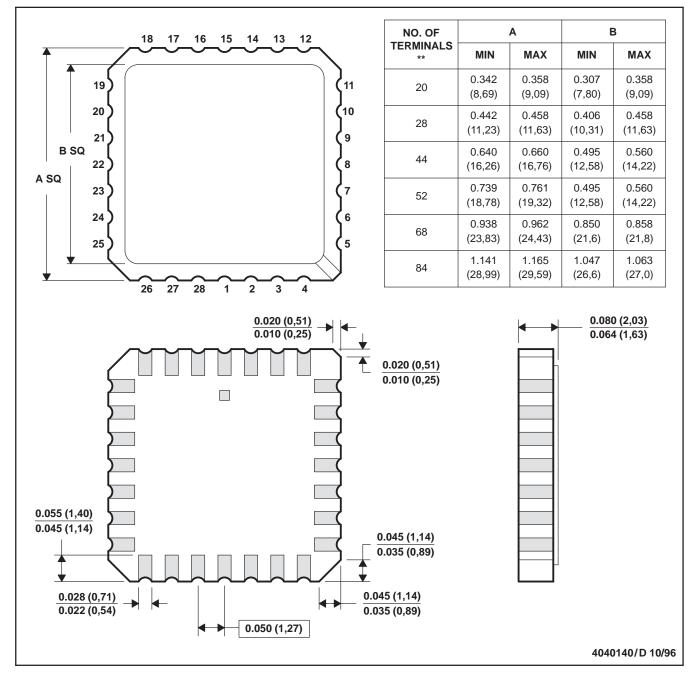

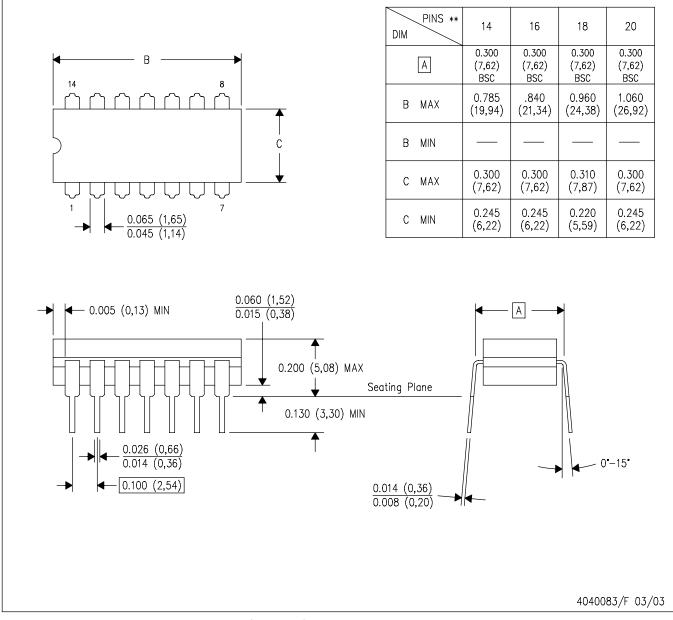

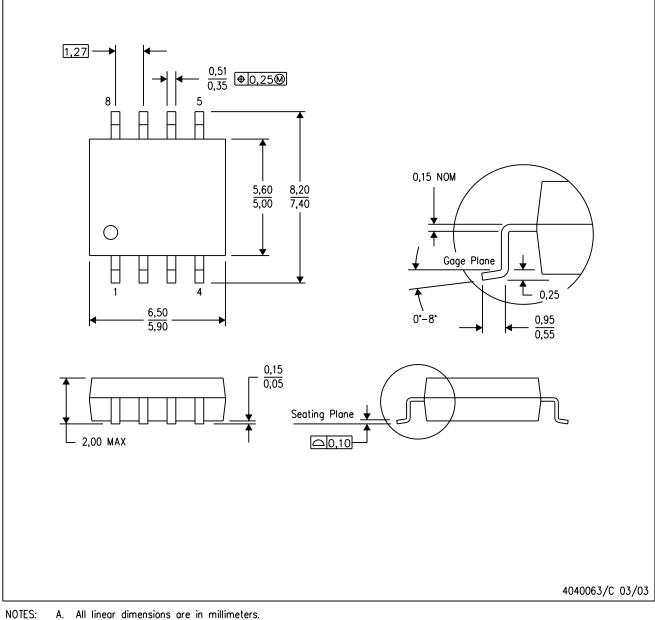

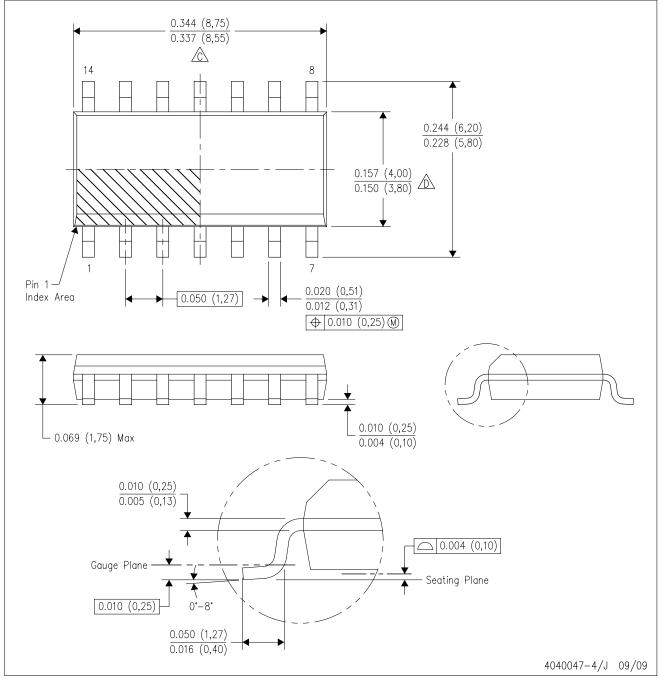

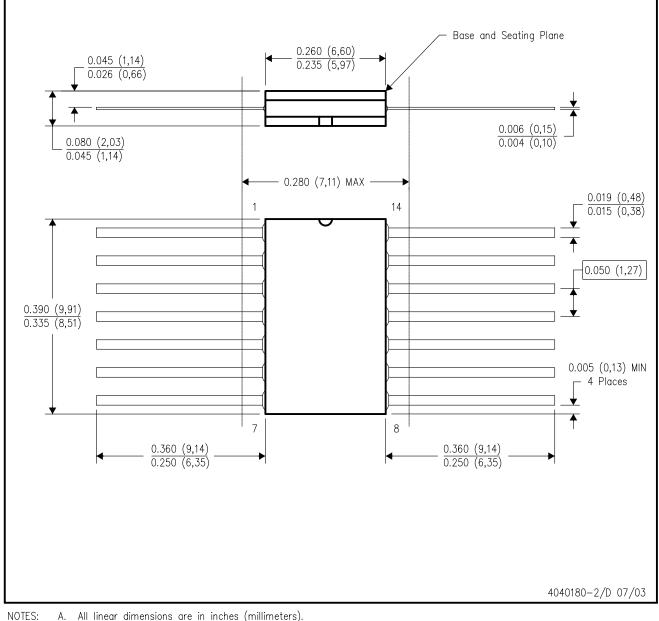

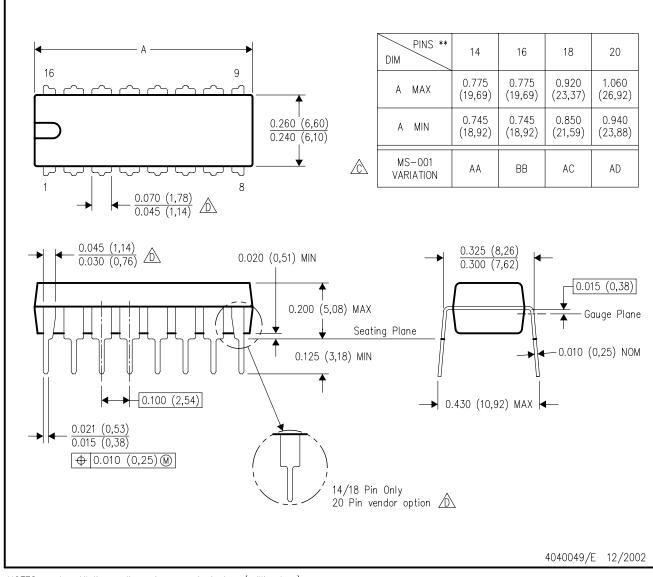

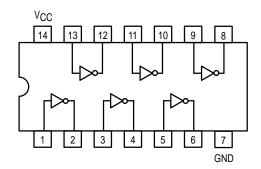

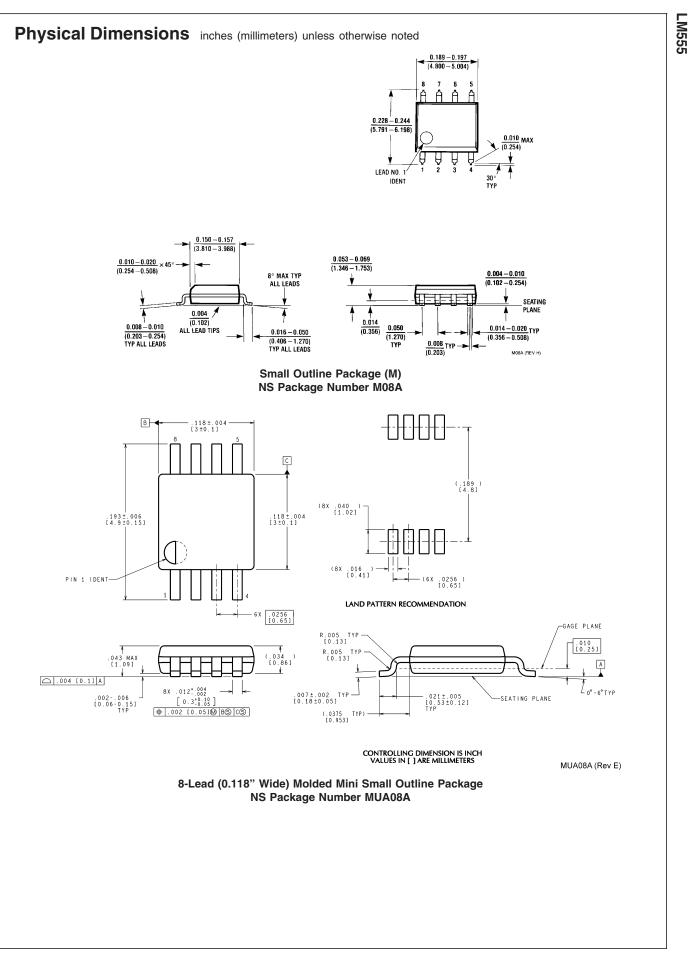

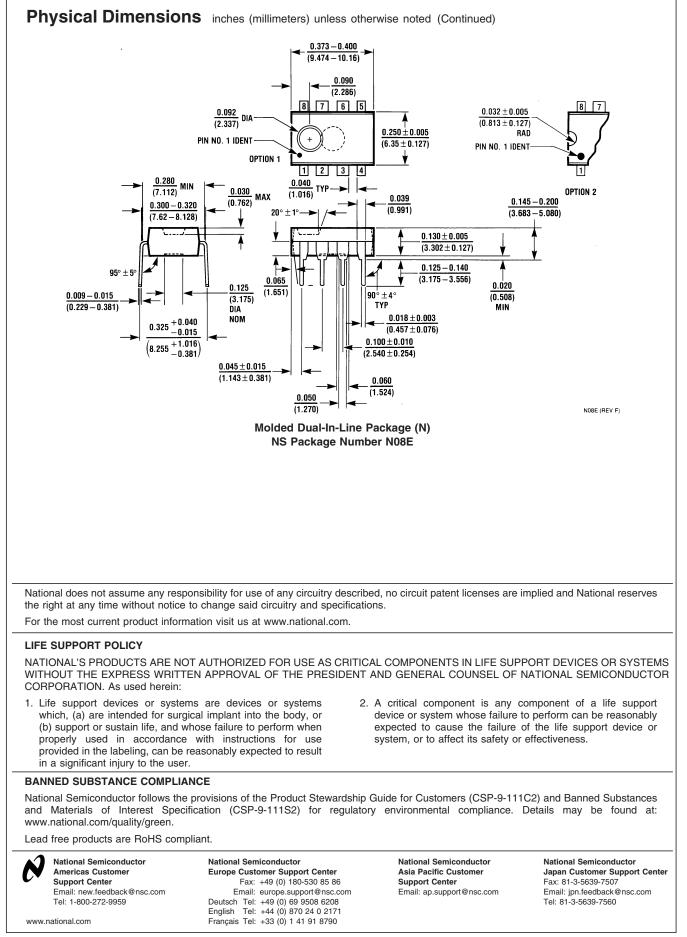

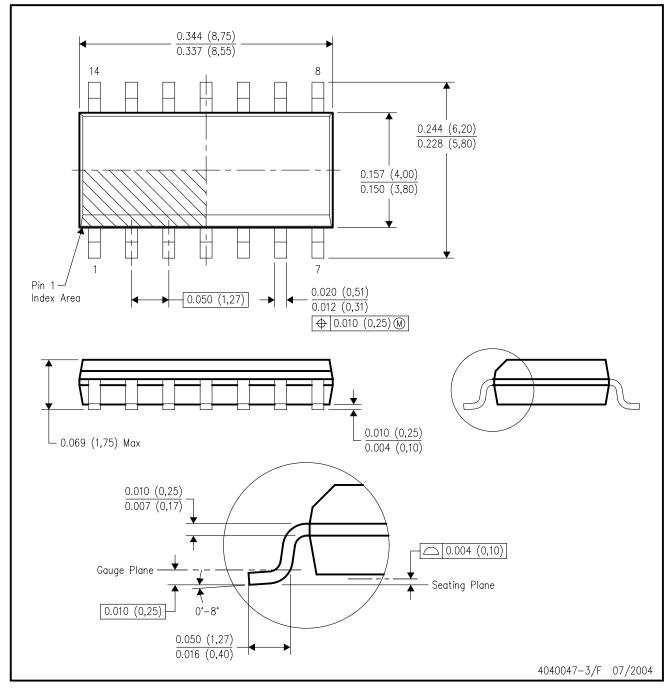

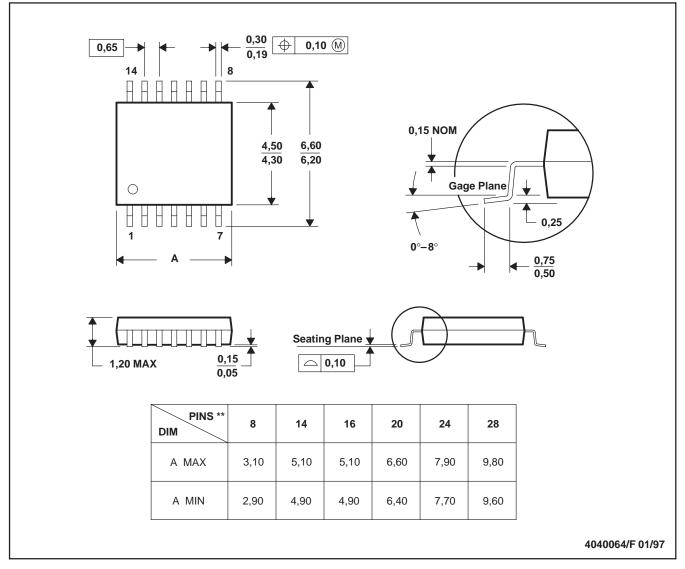

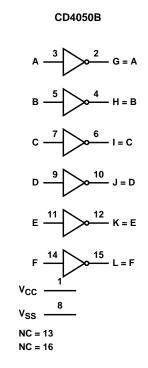

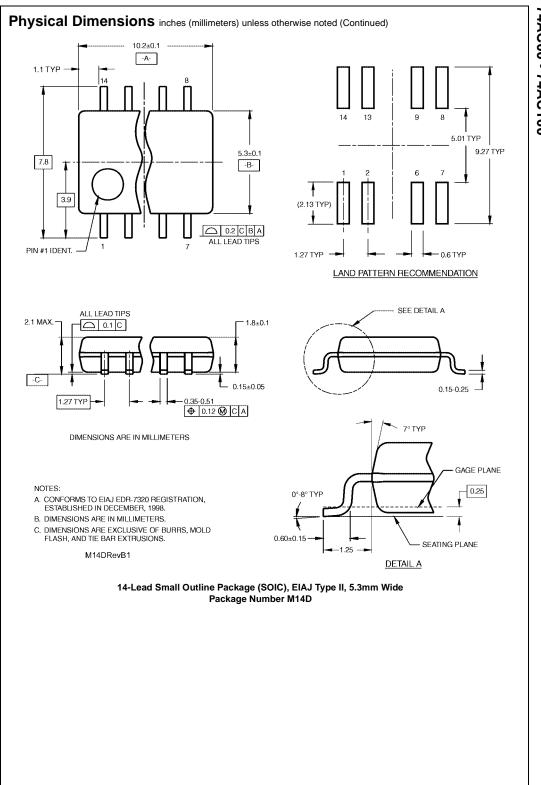

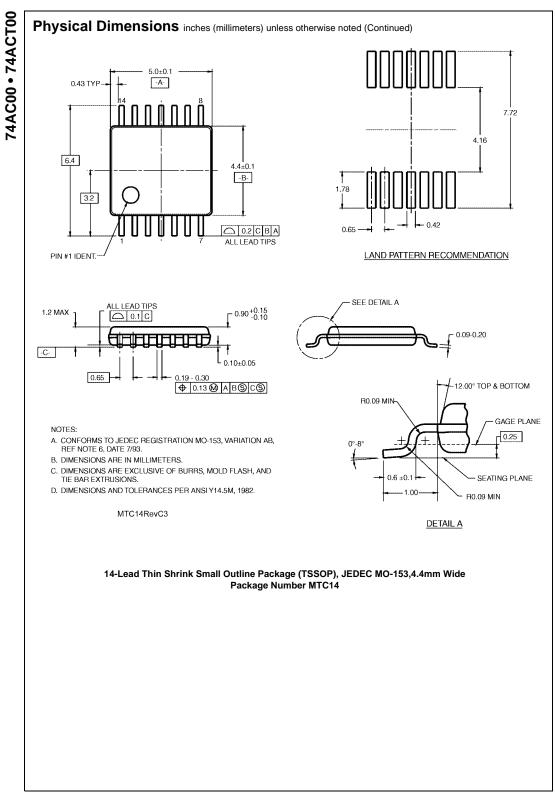

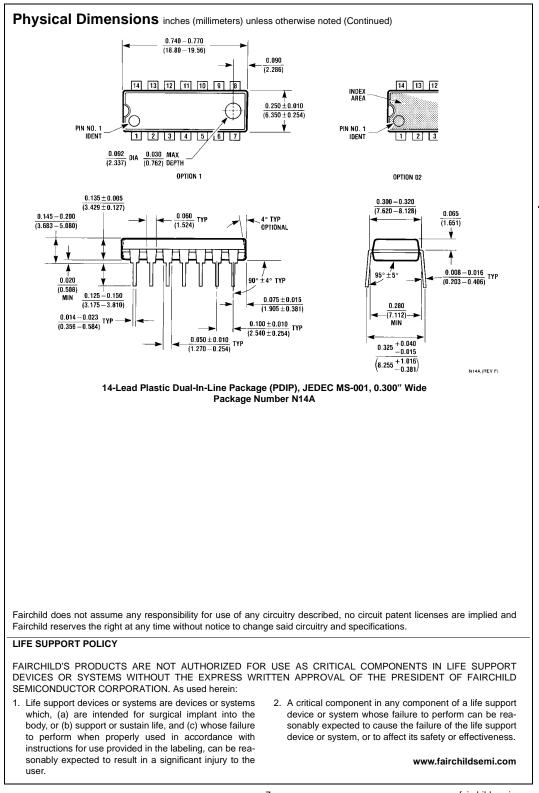

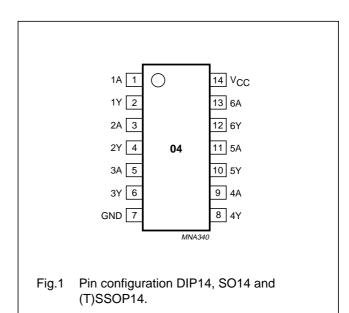

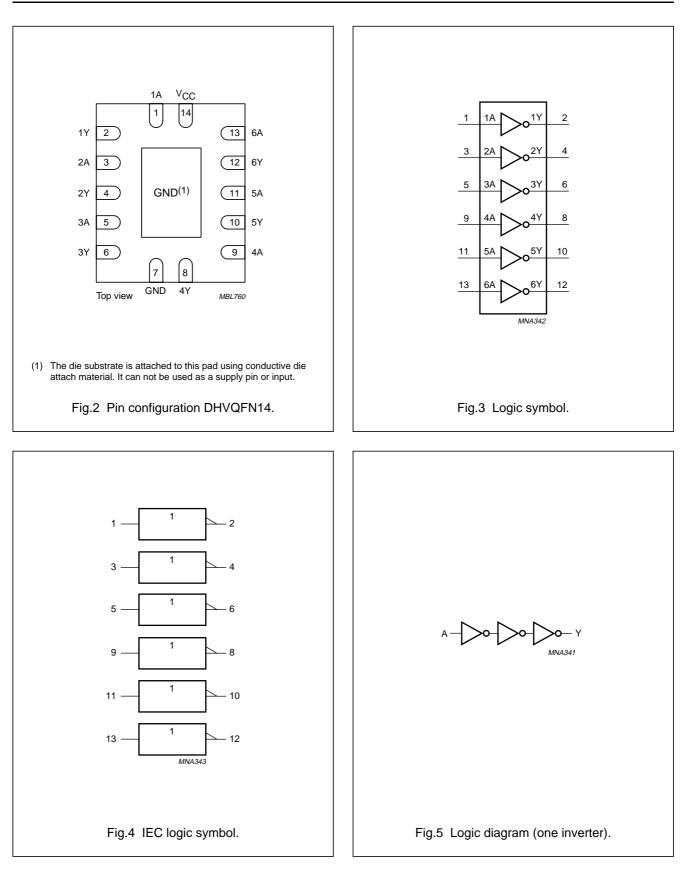

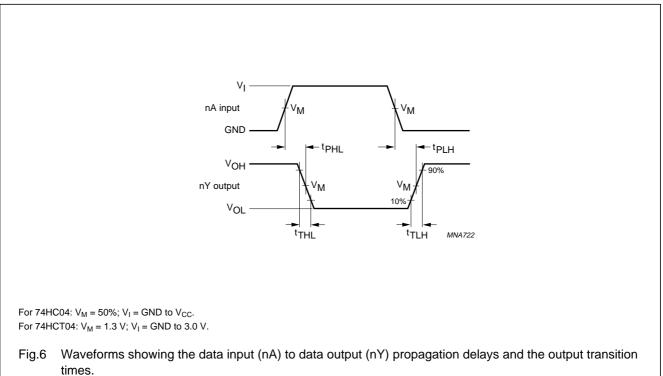

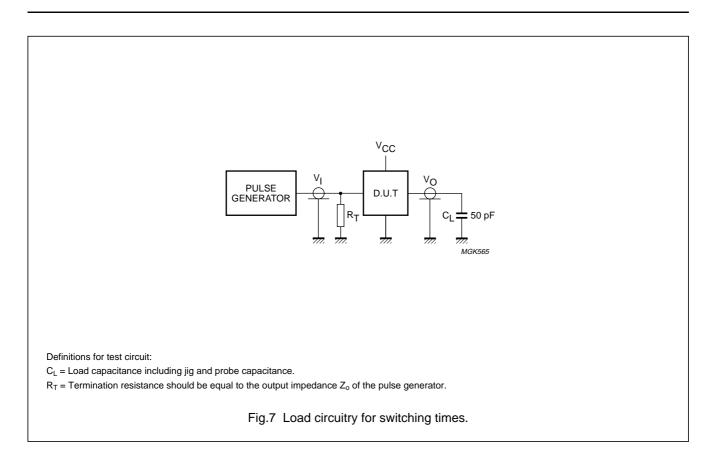

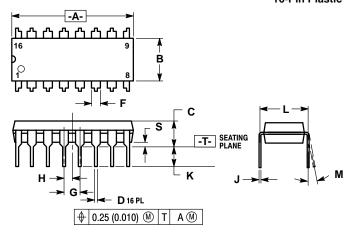

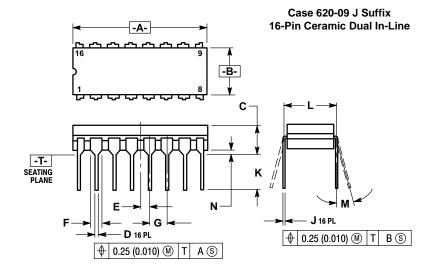

Οι φοιτητές που θα προσέρχονται στο εργαστήριο για την διεξαγωγή της εργαστηριακής άσκησης είναι υποχρεωμένοι να έχουν μελετήσει την άσκηση πιο πριν. Θα πρέπει να έχουν μελετήσει τα κυκλώματα που θα υλοποιήσουν. Επειδή το εργαστήριο Ηλεκτρονικής ΙΙ, έχει να κάνει με την χρήση ολοκληρωμένων κυκλωμάτων οι φοιτητές πρέπει από το σπίτι τους να έχουν διαβάσει τα datasheets των αντίστοιχων ολοκληρωμένων που θα χρησιμοποιήσουν ώστε να ξέρουν τι λειτουργίες αυτό επιτελεί, ποιο ποδαράκι του ολοκληρωμένου αντιστοιχεί σε ποιον ακροδέκτη του κυκλώματος, τι πρέπει να συνδεθεί που και γιατί, κ.ο.κ. Σε αντίθετη περίπτωση δεν θα φτάσει ο χρόνος για να βρεθεί αυτή η πληροφορία κατά την διάρκεια εκπόνησης του εργαστηρίου και επίσης να φτιαχτούν τα κυκλώματα που προβλέπονται και να ληφθούν οι απαραίτητες μετρήσεις.

Επίσης θα πρέπει να έχετε προετοιμάσει το θεωρητικό κομμάτι της άσκησης, στο οποίο εν δυνάμει θα εξετάζεστε, σύμφωνα με αυτά που περιγράφονται στο εδάφιο 3. Κατόπιν παρατηρήσεων πολλών φοιτητών που συμμετείχαν στο εργαστήριο Ηλεκτρονικής Ι (ότι δεν έχουν διαβάσει τα αντίστοιχα θεωρητικά μαθήματα στα οποία βασίζεται το εργαστήριο, και για αυτό δεν μπορούσαν να κατανοήσουν την αντίστοιχη θεωρητική σημασία της), προσδιορίσαμε το εκπαιδευτικό υλικό και της πηγές του ώστε να έρχεστε προετοιμασμένοι κατάλληλα στα εργαστήρια (εδάφιο 3). Το υλικό αυτό προέρχεται είτε από το βιβλίο του μαθήματος των Ψηφιακών Ηλεκτρονικών που διδάσκεται στο Γ εξάμηνο ή από ελεγμένες πηγές του διαδικτύου. Αυτό το υλικό θα δίνεται και σαν παράρτημα στο τέλος αυτού του οδηγού για όσους από εσάς δεν έχετε συνεχή πρόσβαση στο διαδίκτυο. Στο σύγγραμμα που θα προμηθευτείτε στο τέλος κάθε εργαστηριακής άσκησης υπάρχουν τα datasheets των περισσοτέρων από τα ολοκληρωμένα που θα χρησιμοποιήσετε στα πλαίσια των εργαστηριακών ασκήσεων. Υπάρχουν όμως και άλλα που αν και θα χρειαστείτε δεν υπάρχουν μέσα στο σύγγραμμα. Αυτά θα τα βρείτε πολύ εύκολα κάνοντας μια αναζήτησης στο διαδίκτυο (π. μέσω google), με όρους αναζήτησης τον τύπο του ολοκληρωμένου κυκλώματος, ακολουθούμενο από την λέξη datasheet. Π.χ. για το χρονιστή (timer) 555, που όπως αναφέρεται στην εργαστηριακή άσκηση 5, χρησιμοποιείται μέσω του ολοκληρωμένου LM555, αρκεί να γράψουμε σαν όρο αναζήτησης το "LM555 datasheet". Λογικά το datasheet που ψάχνεται θα βρίσκεται στη πρώτες επιλογές. Στα πλαίσια του εν λόγω οδηγού «Μελέτης και εκπόνησης Εργαστηρίου Ηλεκτρονικής ΙΙ», θα γίνει προσπάθεια ώστε στο τέλος του να υπάρχουν τα datasheets όλων των ολοκληρωμένων που θα χρειαστείτε.

Είναι πολύ ΣΗΜΑΝΤΙΚΟ, να έχετε μελετήσει τα datasheet των ολοκληρωμένων κάθε άσκησης πιο πριν, ώστε να ξέρετε σε τι αντιστοιχεί ο κάθε ακροδέκτης του ολοκληρωμένου και να μπορέσετε να φτιάξετε έστω τα κυκλώματα των εργαστηριακών ασκήσεων. Τα εν λόγω datasheet, δεν είναι ανάγκη να τα διαβάζετε στο σύνολο τους. Απλά να παίρνεται μόνο της απαραίτητες πληροφορίες για αυτά που αναφέρθηκαν πιο πάνω ώστε να μπορείτε να ανταποκριθείτε στης ανάγκες του εργαστηρίου σύμφωνα με τα ζητούμενα σε κάθε άσκηση.

#### 3. Διδακτικό Υλικό Προεργασίας ανά Εργαστηριακή Άσκηση

Η εργαστηριακή άσκηση 1, περιέχει κυκλώματα που περιλαμβάνουν τελεστικούς ενισχυτές. Όλες της απαραίτητες πληροφορίες που θα χρειαστείτε τόσο για τα πρακτικά όσο για τα θεωρητικά ζητήματα του εργαστηρίου που αφορούν τους τελεστικούς ενισχυτές, θα της βρείτε στα ακόλουθα δύο links:

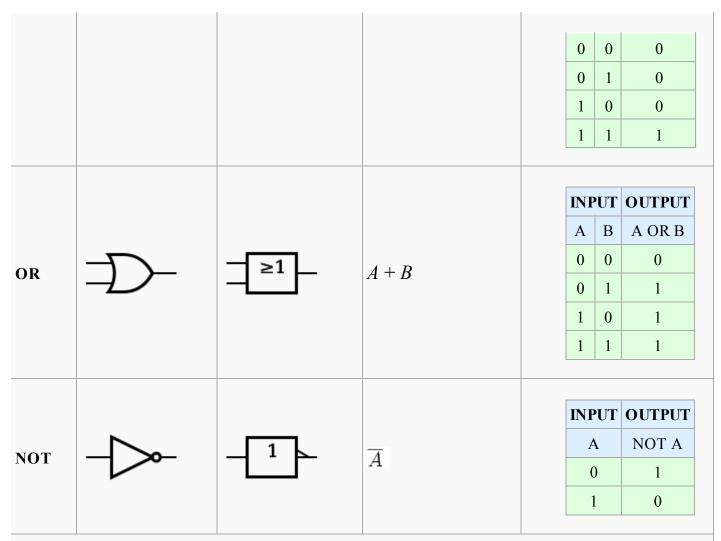

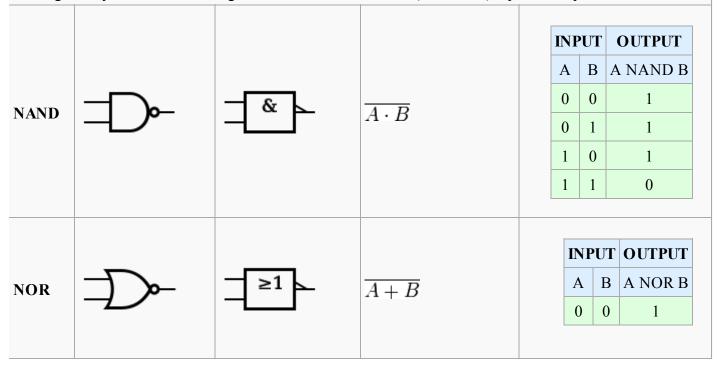

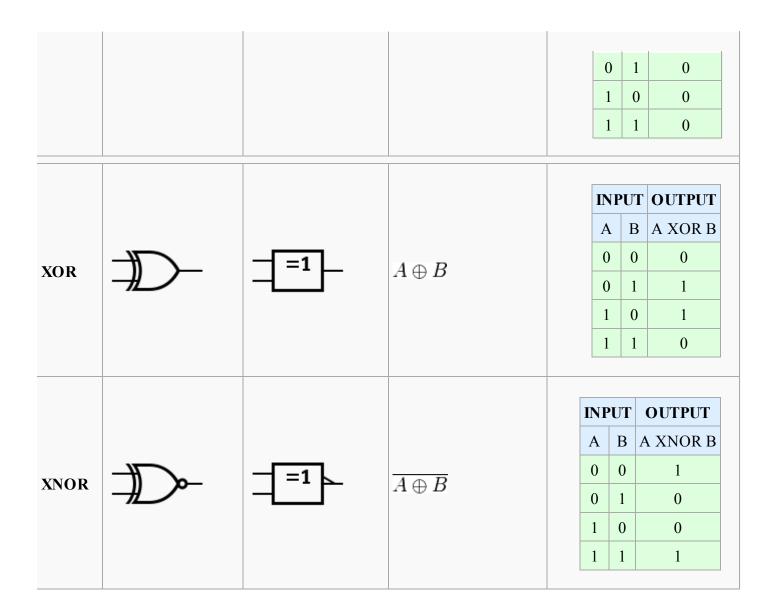

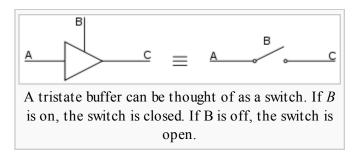

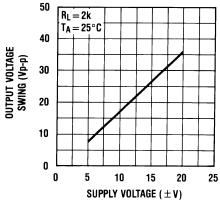

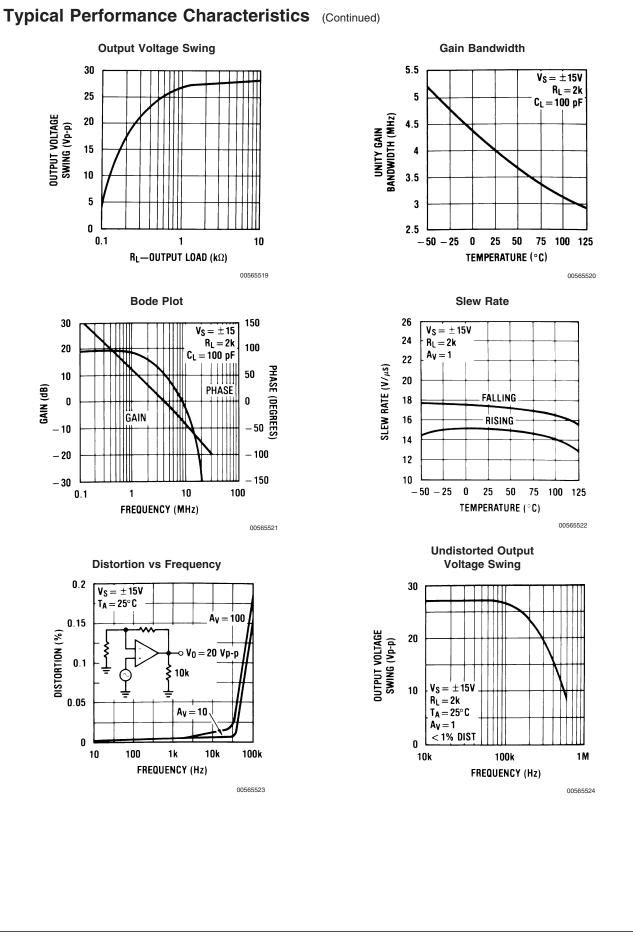

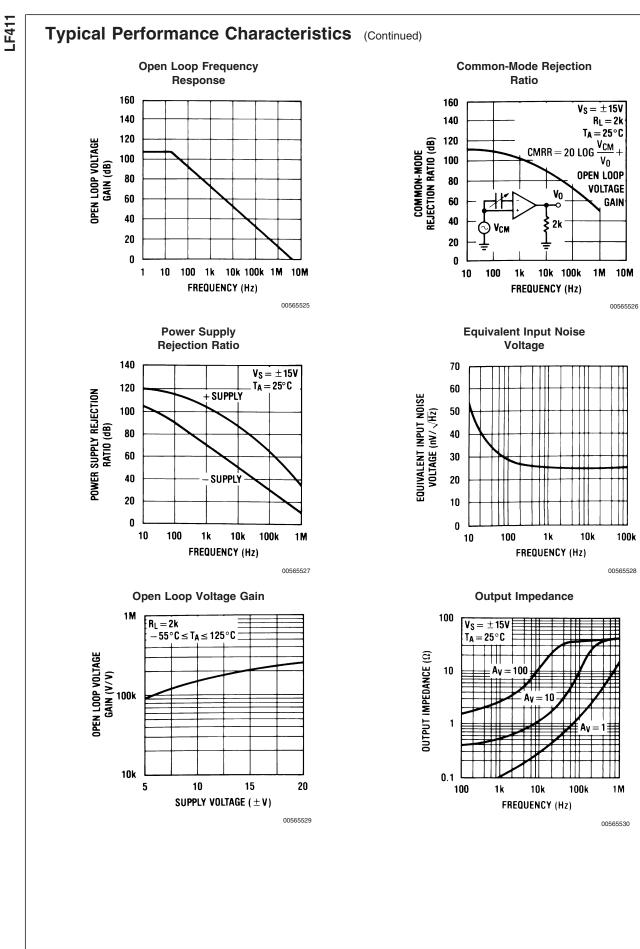

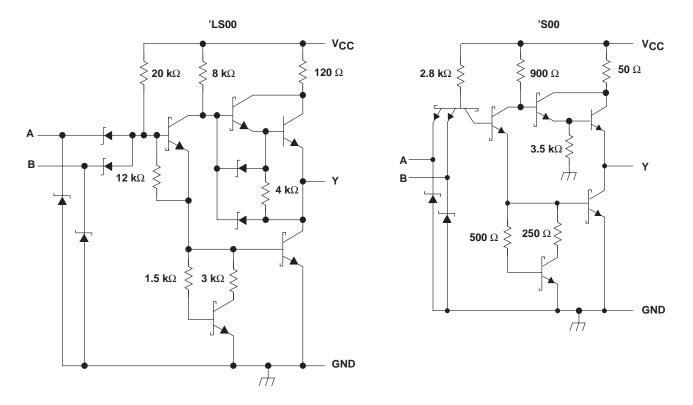

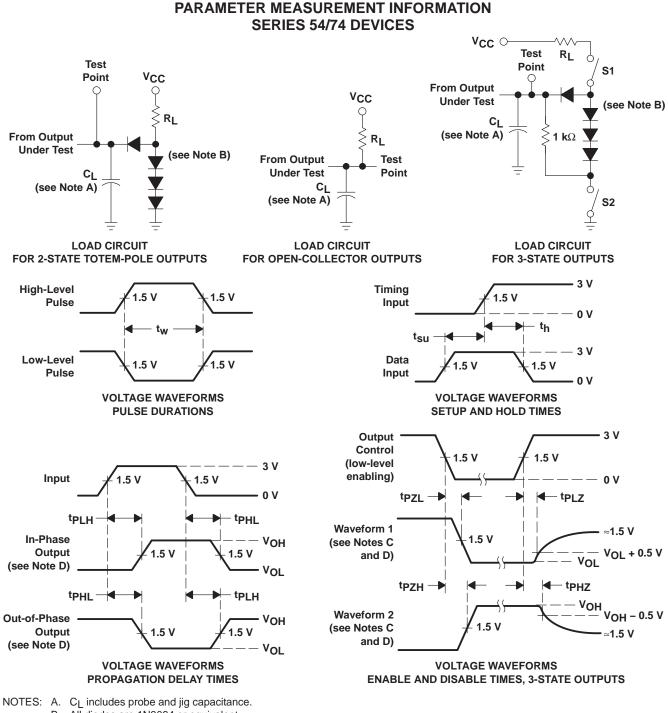

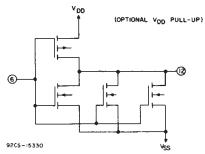

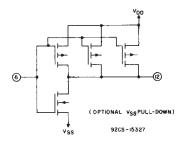

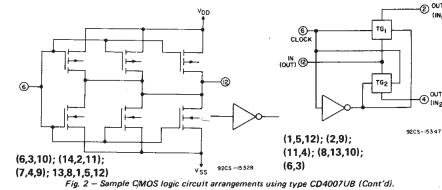

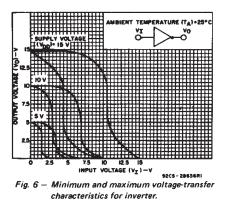

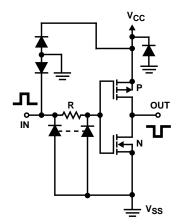

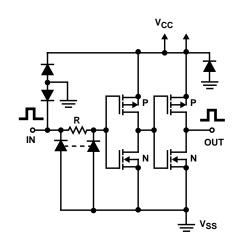

http://en.wikipedia.org/wiki/Operational\_amplifier http://en.wikipedia.org/wiki/Operational\_amplifier\_applications

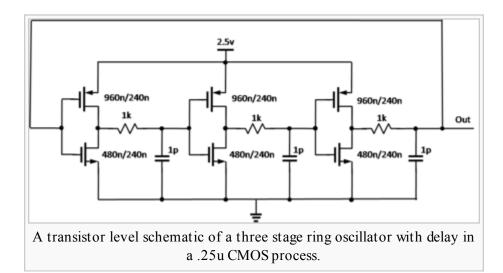

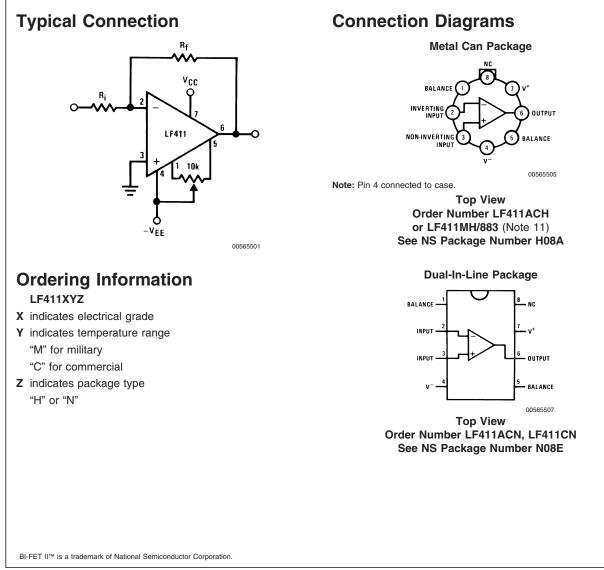

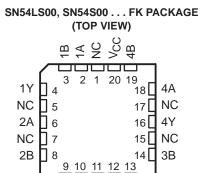

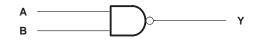

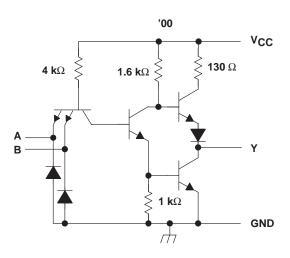

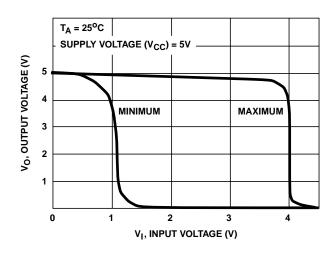

Σε αυτά τα links, εξηγούνται εύκολα και κατανοητά όλα όσα απατούνται. Τελεστικούς ενισχυτές έχετε διδαχθεί και σε μαθήματα προηγούμενων εξαμήνων οπότε προφανώς σας καλύπτουν και τα αντίστοιχα συγγράμματα που χρησιμοποιήσατε σε αυτά τα μαθήματα. Θα χρειαστεί επίσης να μελετήσατε τα datasheets των ολοκληρωμένων LF411 και 741 που χρησιμοποιούνται στα πλαίσια της άσκησης. Η εργαστηριακή άσκηση 2, περιέχει κυκλώματα που περιλαμβάνουν ψηφιακές πύλες, ταλαντωτές δακτυλίου (ring oscillators), πύλες TTL, πύλες CMOS και πύλες CMOS τριών καταστάσεων. Από άποψη υλικού που πρέπει να μελετήσετε είναι η πλέον εκτενής. Αυτό όμως θα το βρείτε μπροστά σας αφού και οι υπόλοιπες εργαστηριακές ασκήσεις στηρίζονται σε αυτές της γνώσεις. Έτσι εάν καταλάβετε της βασικές έννοιες αυτής της άσκησης θα έχετε ένα πολύ καλό εφόδιο για την συνέχεια του εργαστηρίου και λιγότερο διάβασμα στης επόμενες εργαστηριακές ασκήσεις.

Αυτά που θα χρειαστεί να μελετήσετε είναι τα αντίστοιχα εδάφια από το βιβλίο του μαθήματος των Ψηφιακών Ηλεκτρονικών του Γ εξαμήνου. Σε σχέση με το βιβλίο του κ. Λιούπη για τα Ψηφιακά Ηλεκτρονικά, θα πρέπει να μελετήσετε της σελίδες 23 έως 38 και 59 έως 63. το εν λόγω βιβλίο μπορεί να βρεθεί στην ηλεκτρονική διεύθυνση:

http://aiolos.cti.gr/gr/faculty/psifil/

και οι σελίδες που αναφέρονται πιο πάνω προς μελέτη ανήκουν στα κεφάλαια 2 και 3 αντίστοιχα. Πολλές και χρήσιμες πληροφορίες σχετικά με της λογικές πύλες, της πύλες τριών καταστάσεων κ.ο.κ, τους ταλαντωτές δακτυλίου κ.α. μπορείτε να βρείτε και στης ακόλουθες ιστοσελίδες:

http://en.wikipedia.org/wiki/Logic\_gate http://en.wikipedia.org/wiki/Ring\_oscillator

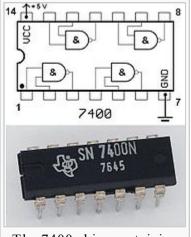

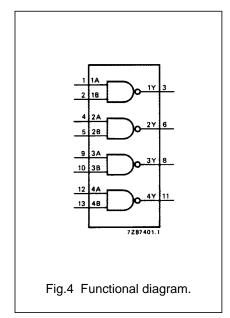

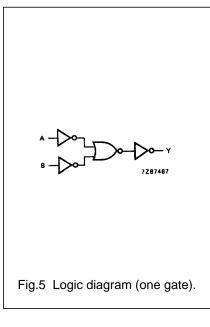

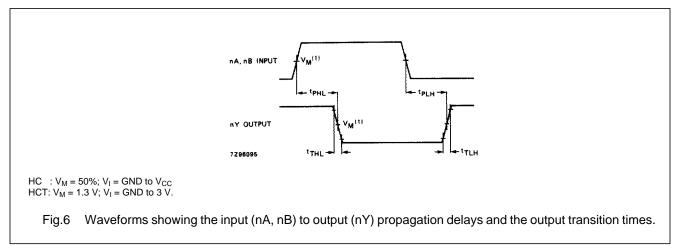

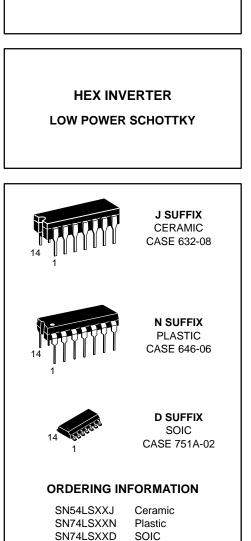

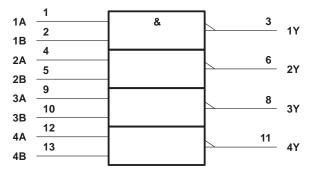

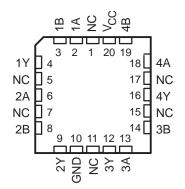

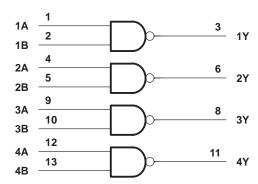

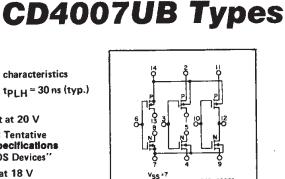

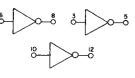

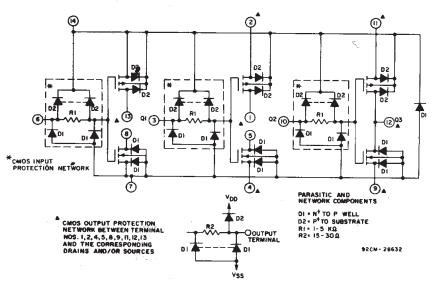

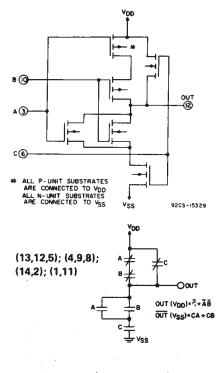

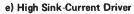

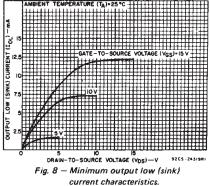

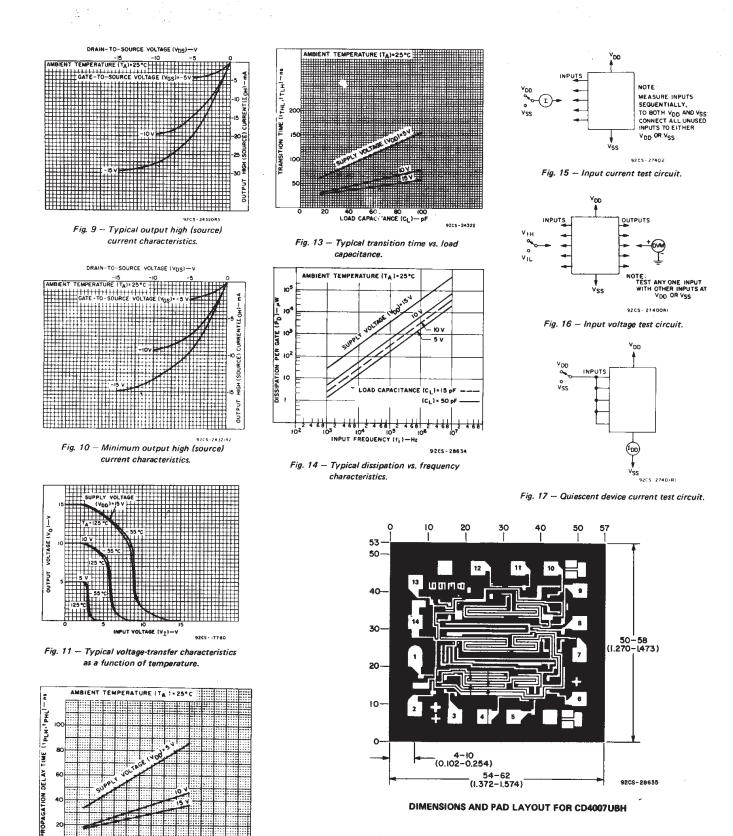

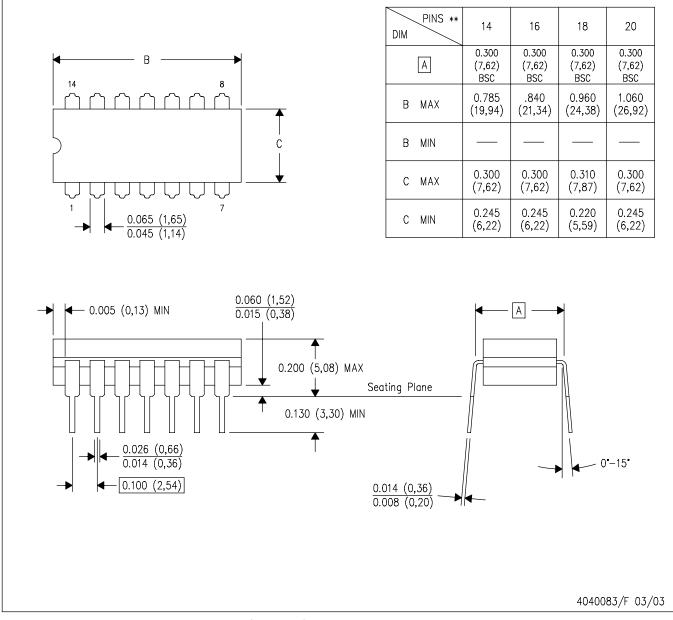

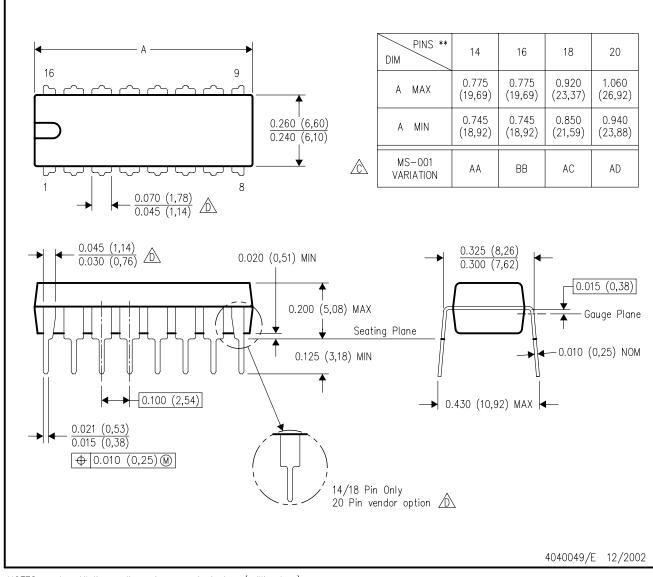

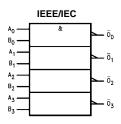

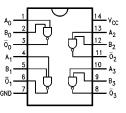

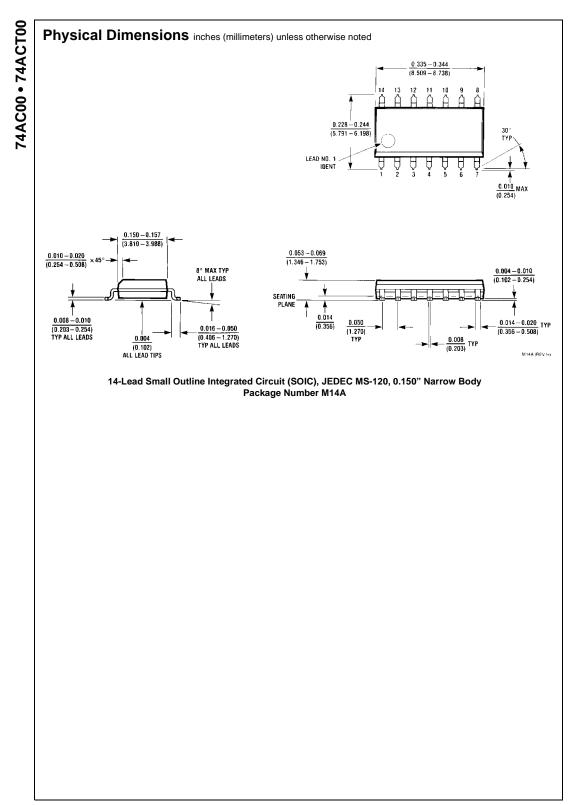

Προφανώς μπορείτε να χρησιμοποιήσετε και συγγράμματα που έχετε πάρει από την σχολή και καλύπτουν τα παραπάνω θεματικά αντικείμενα. Θα χρειαστεί επίσης να μελετήσατε τα datasheets των ολοκληρωμένων 74LS00, 74HC00, και CD4007 που χρησιμοποιούνται στα πλαίσια της άσκησης.

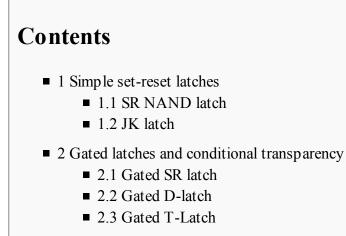

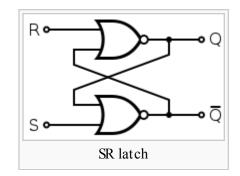

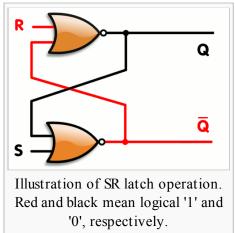

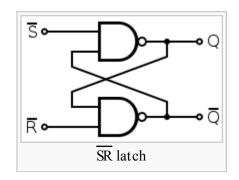

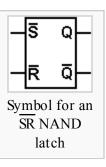

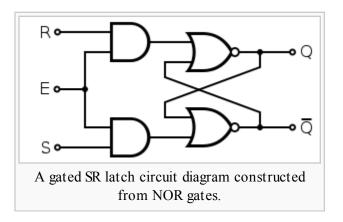

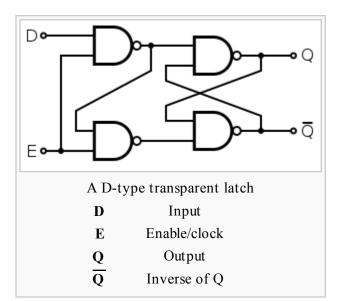

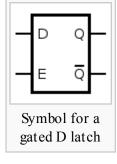

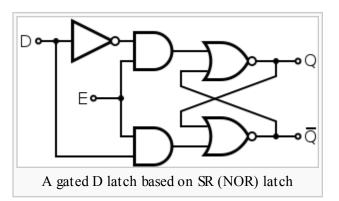

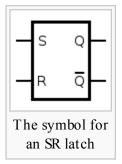

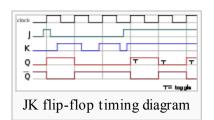

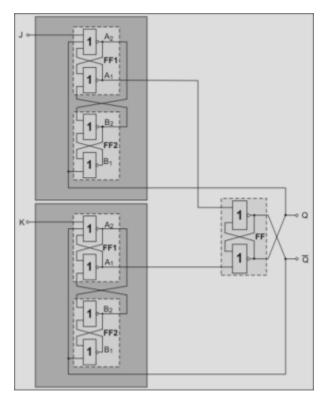

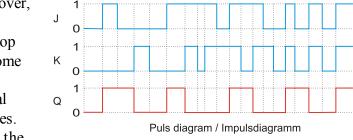

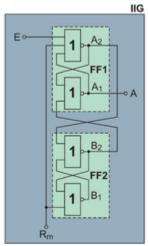

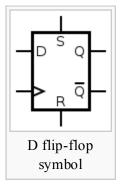

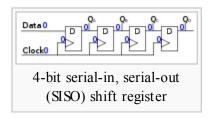

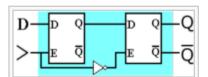

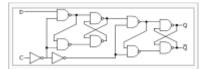

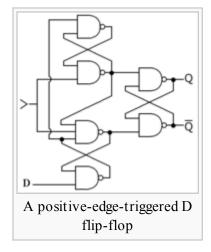

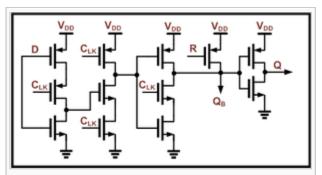

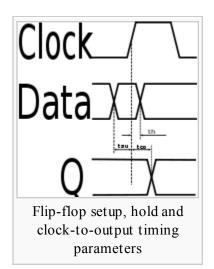

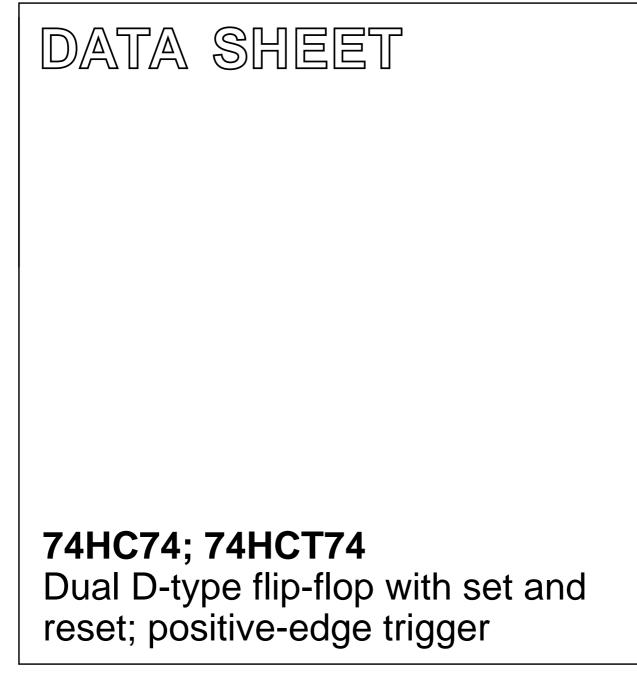

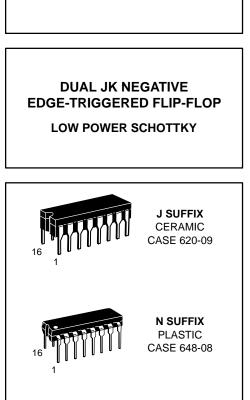

Η εργαστηριακή άσκηση 3, περιέχει κυκλώματα που περιλαμβάνουν στοιχεία αποθήκευσης όπως latches, flip-flop τύπου D, T και J-K. Αυτά που θα χρειαστεί να διαβάσετε και να ξέρετε για την εκπόνηση του εργαστηρίου, βρίσκονται στης ακόλουθες ιστοσελίδες

http://en.wikipedia.org/wiki/Latch\_(electronics) http://en.wikipedia.org/wiki/Flip-flop (electronics)

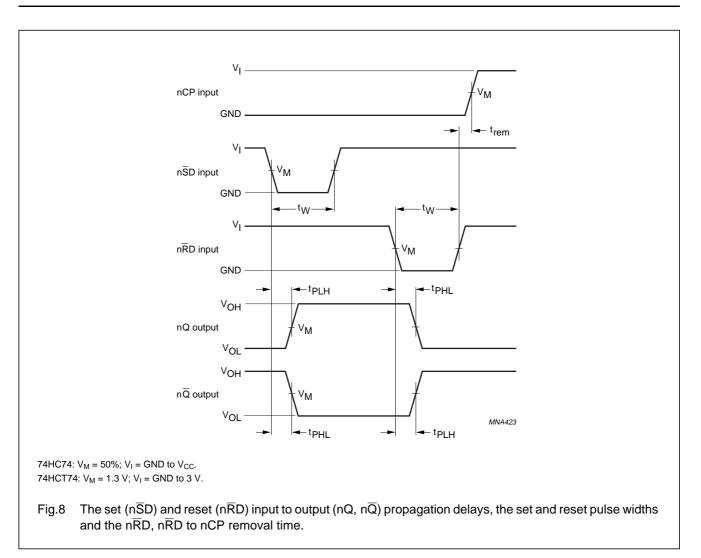

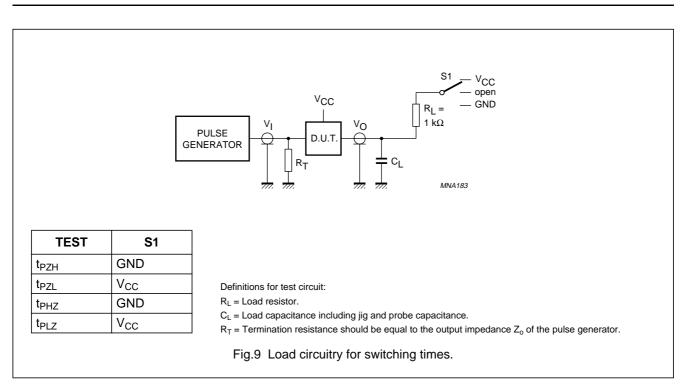

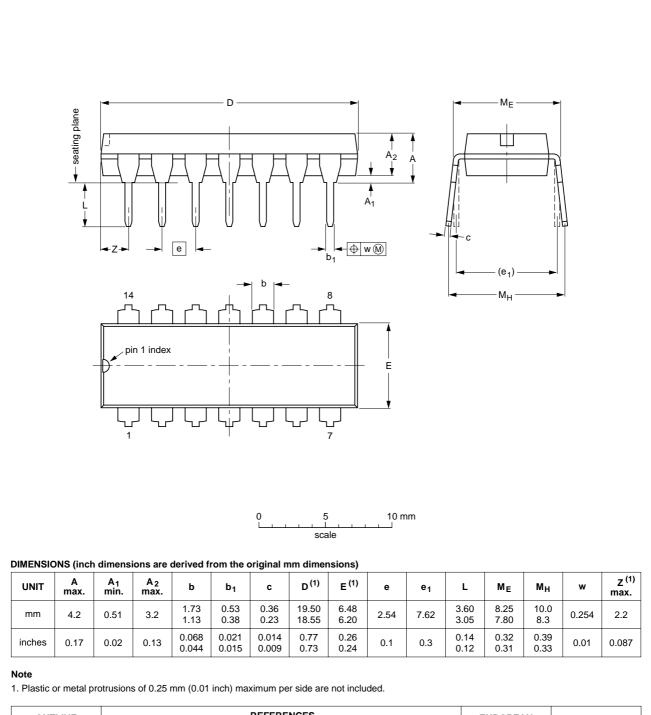

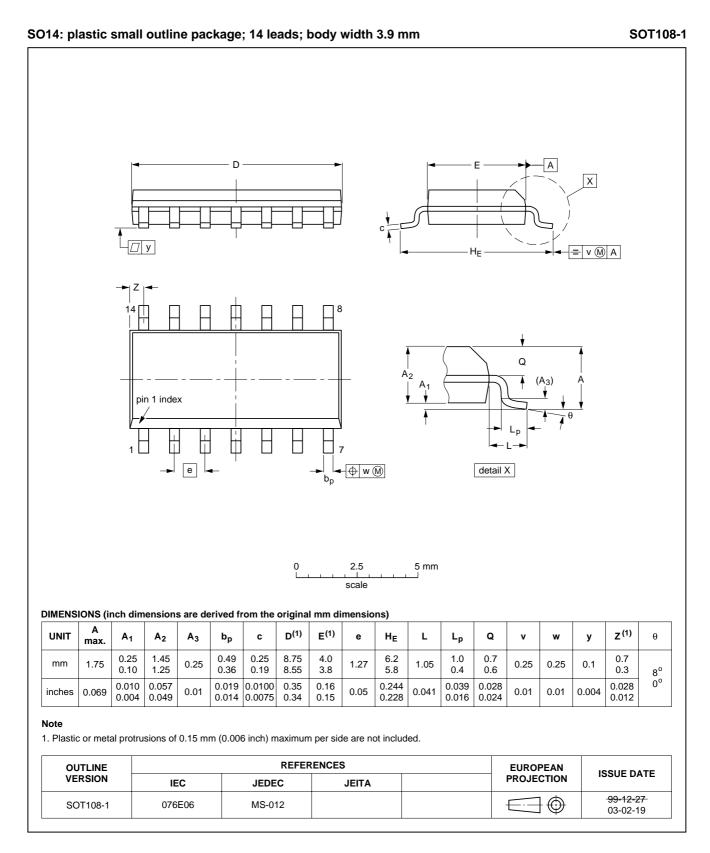

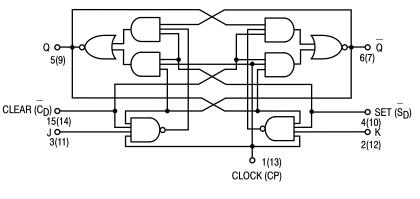

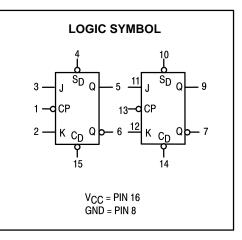

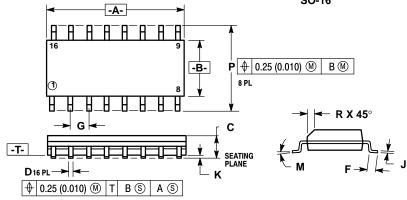

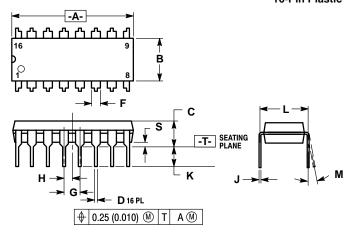

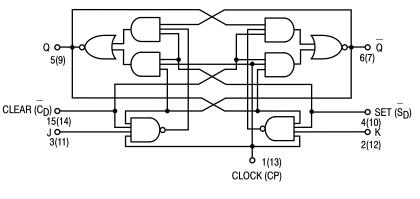

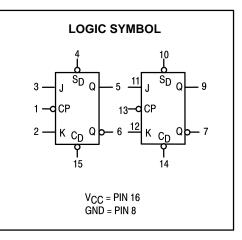

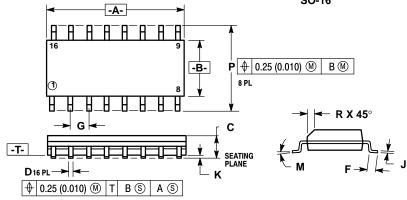

Προφανώς μπορείτε να χρησιμοποιήσετε και συγγράμματα που έχετε πάρει από την σχολή και καλύπτουν τα παραπάνω θεματικά αντικείμενα. Θα χρειαστεί επίσης να μελετήσατε τα datasheets των ολοκληρωμένων 74HC00, 74HC74, 74LS112, 74HC175, και 74HC08 που χρησιμοποιούνται στα πλαίσια της άσκησης.

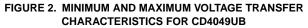

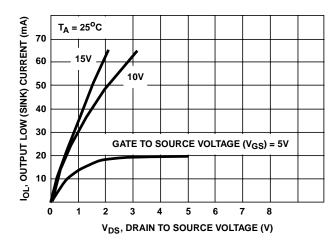

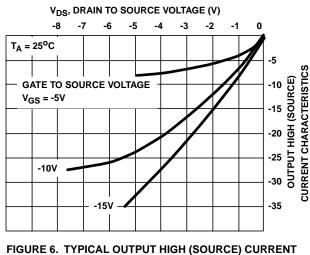

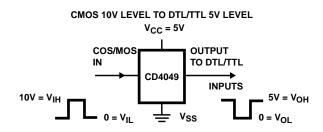

Η εργαστηριακή άσκηση 4, διαπραγματεύεται την διασύνδεση λογικών πυλών ίδιων και διαφορετικών οικογενειών π.χ. διασύνδεση πυλών CMOS και TTL. Σε αυτή την άσκηση είναι απαραίτητο να γνωρίζετε αυτά που αναφέρθηκαν στην εργαστηριακή άσκηση 2 για της πύλες TTL και πύλες CMOS δηλαδή από το βιβλίο του μαθήματος των Ψηφιακών Ηλεκτρονικών του κ. Λιούπη της σελίδες 23 έως 38 και 59 έως 63. που ανήκουν στα κεφάλαια 2 και 3 αντίστοιχα.

Το μόνο νέο κομμάτι που θα πρέπει να μελετήσετε έχει να κάνει με το αντίστοιχο 4° κεφάλαιο του ίδιου βιβλίου που αφορά ακριβώς την διασύνδεση λογικών πυλών διαφορετικών οικογενειών. Έτσι πρέπει να διαβάσετε της σελίδες 91-95 από το αντίστοιχο τέταρτο κεφάλαιο.

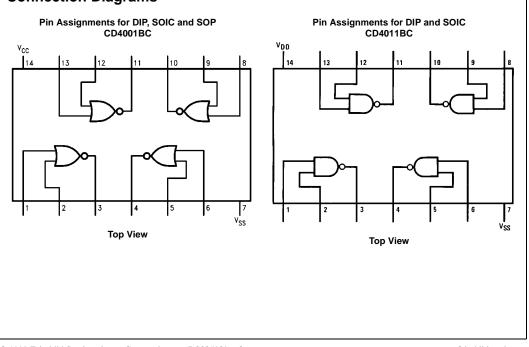

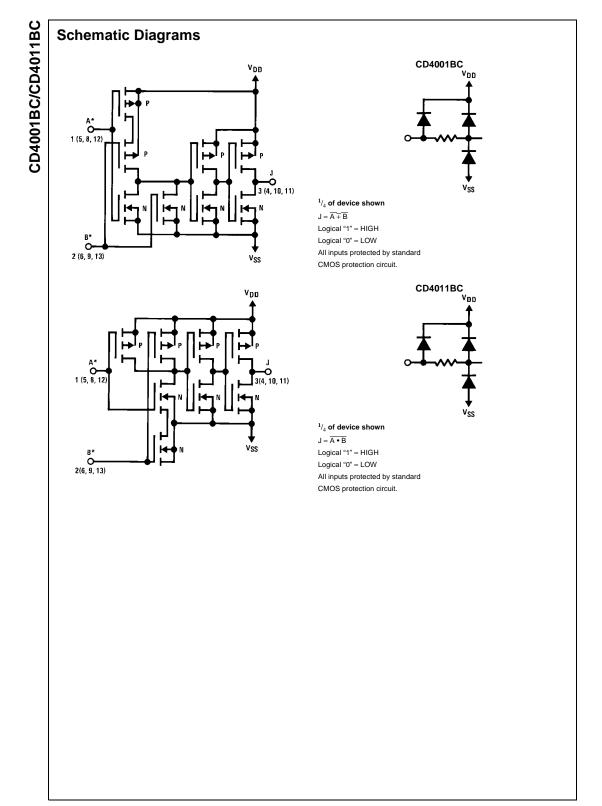

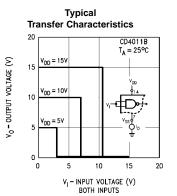

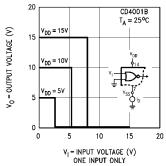

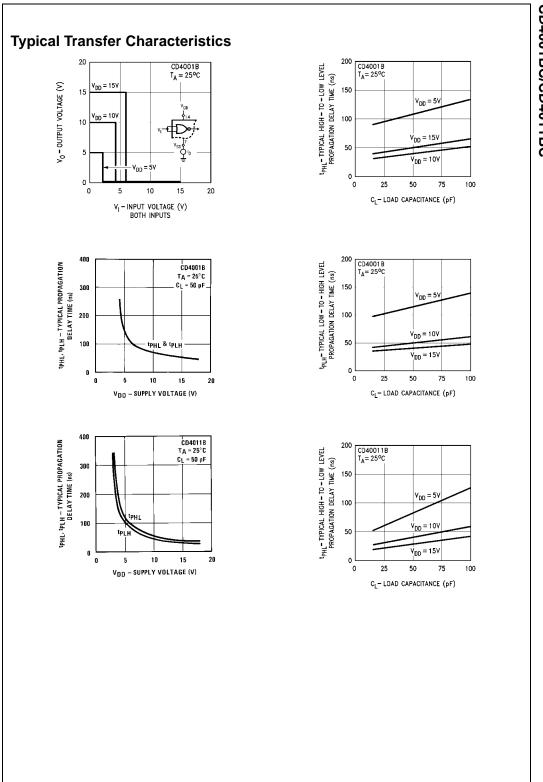

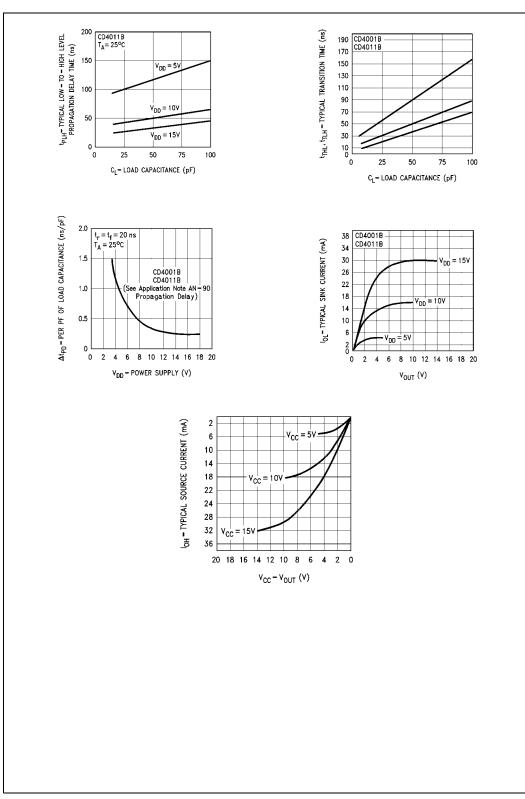

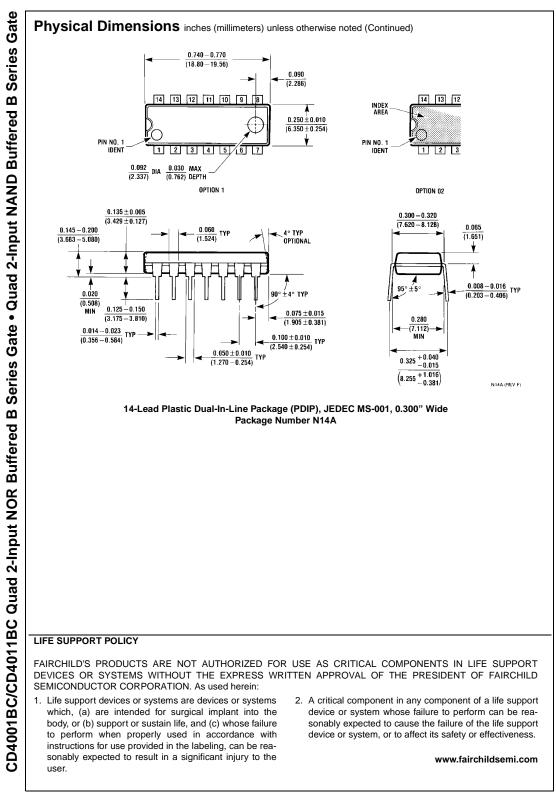

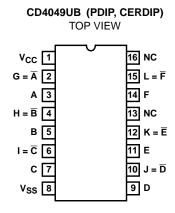

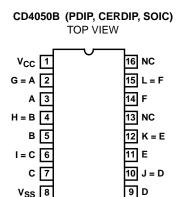

Θα χρειαστεί επίσης να μελετήσατε τα datasheets των ολοκληρωμένων 74LS00, 74HC00, 74HCT00, 74LS04, 74HC04, CD4001B και CD400, που χρησιμοποιούνται στα πλαίσια της άσκησης.

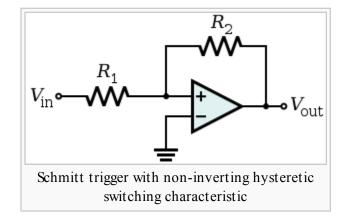

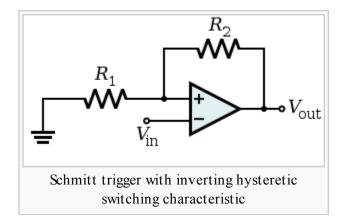

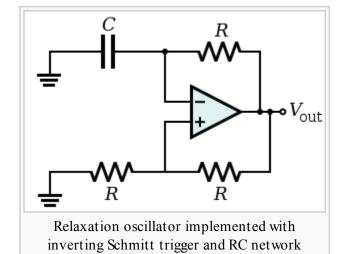

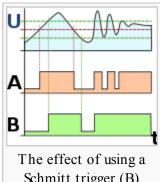

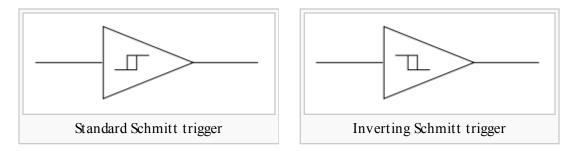

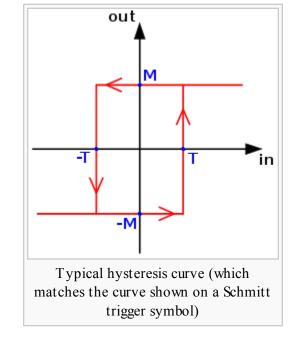

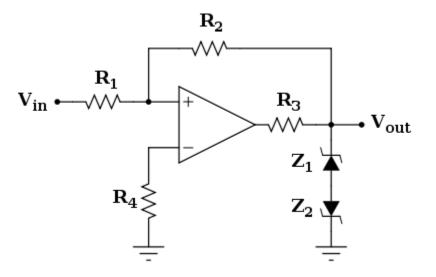

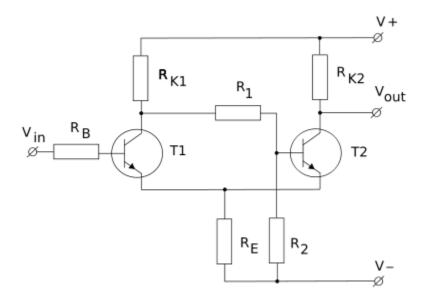

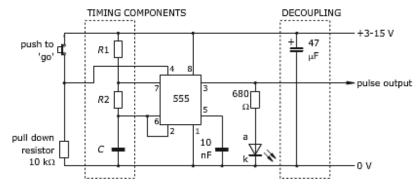

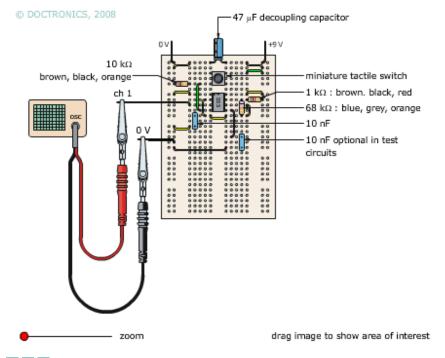

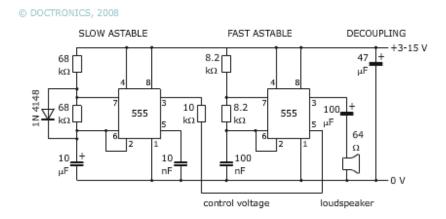

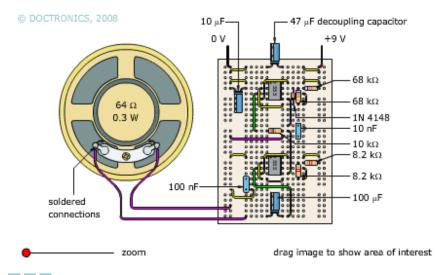

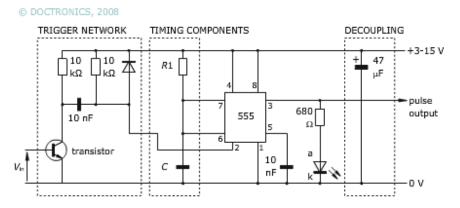

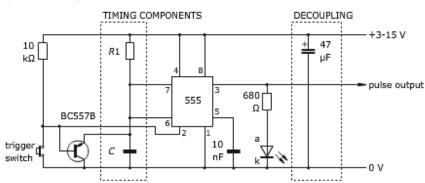

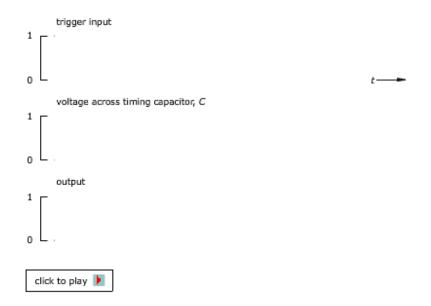

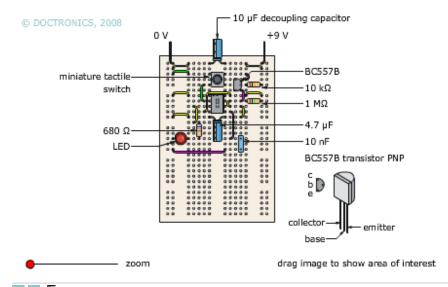

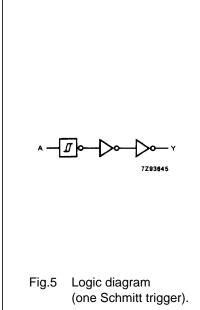

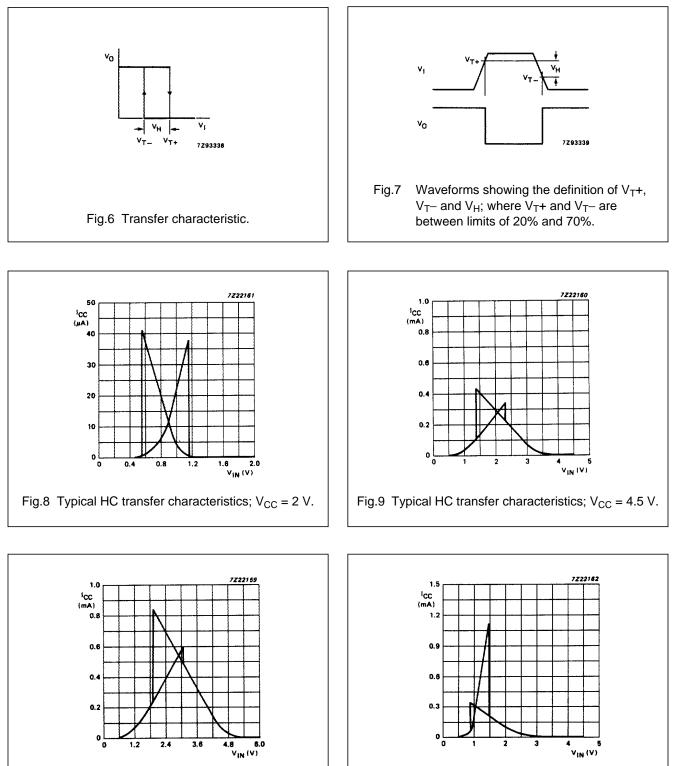

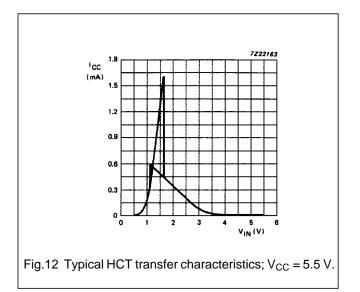

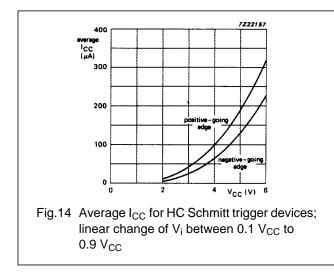

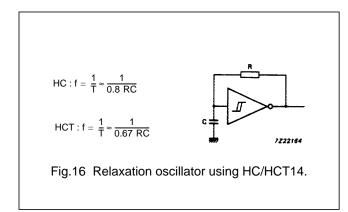

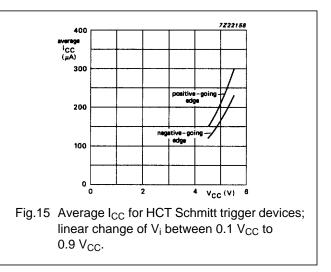

Η εργαστηριακή άσκηση 5, περιέχει κυκλώματα που περιλαμβάνουν σκανδαλιστές Schmitt trigger και κυκλώματα χρονιστών. Για τον σκανδαλιστή Schmitt trigger, μπορείτε να διαβάσετε αρκετά πράγμα από της σελίδες 69-70 του βιβλίου του κ. Λιούπη για τα Ψηφιακά Ηλεκτρονικά καθώς επίσης και από την ακόλουθη ιστοσελίδα:

#### http://en.wikipedia.org/wiki/Schmitt\_trigger

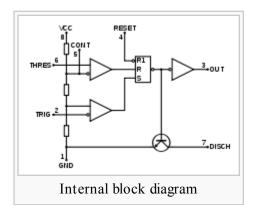

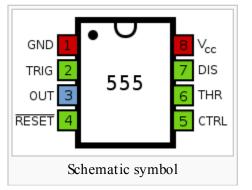

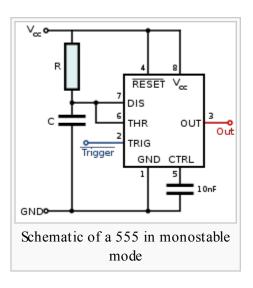

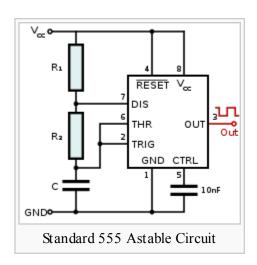

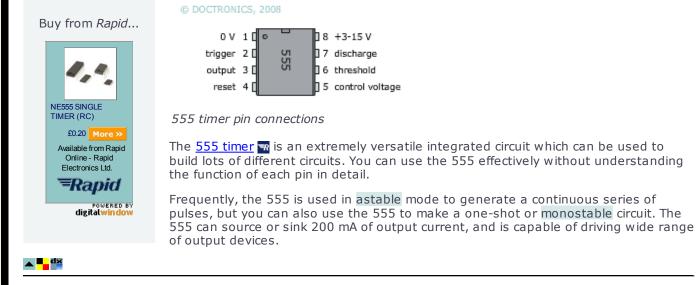

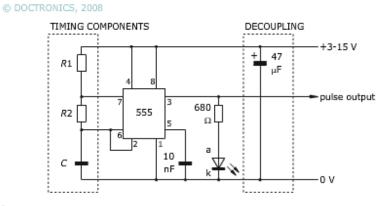

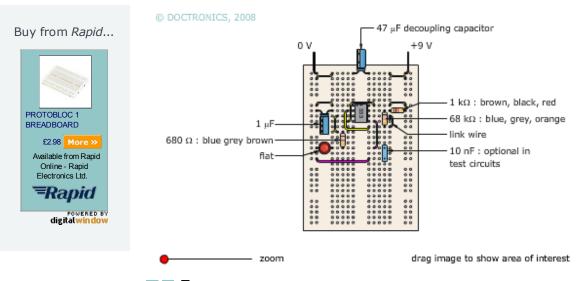

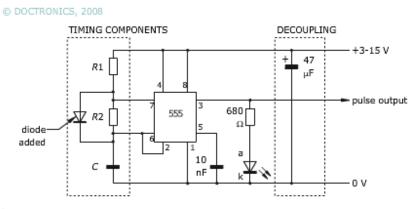

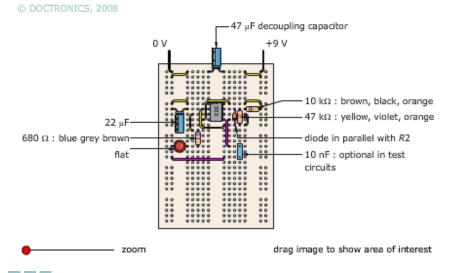

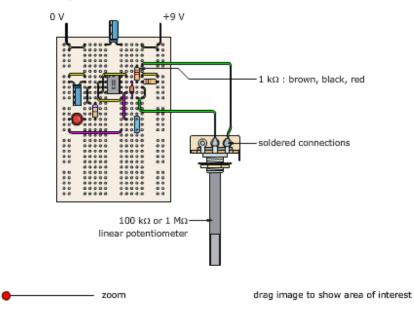

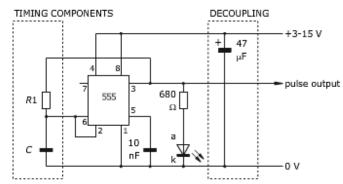

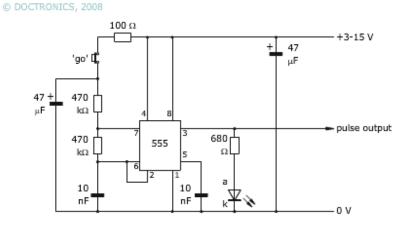

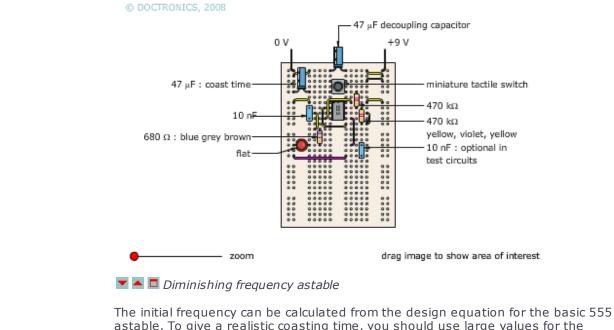

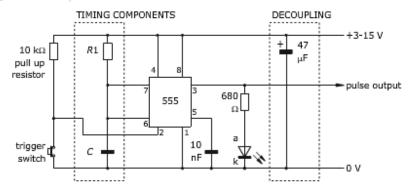

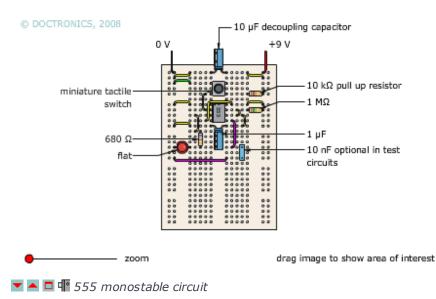

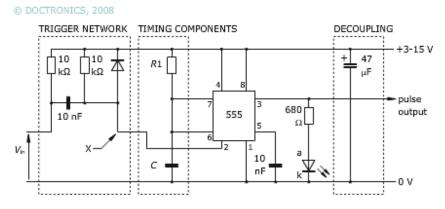

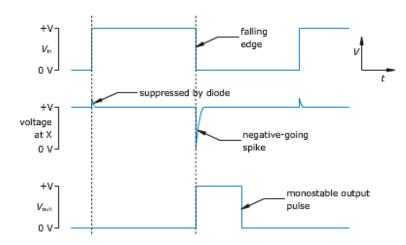

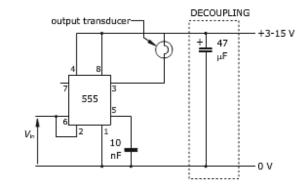

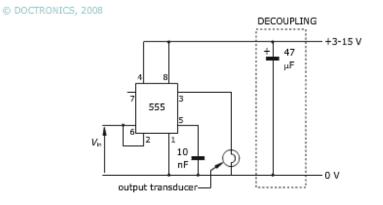

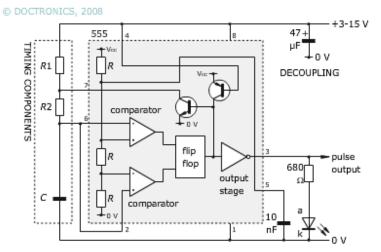

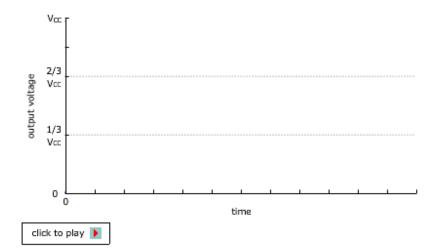

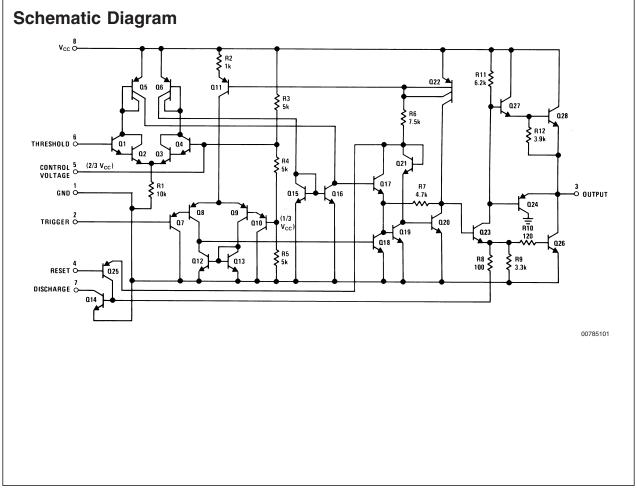

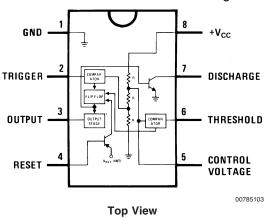

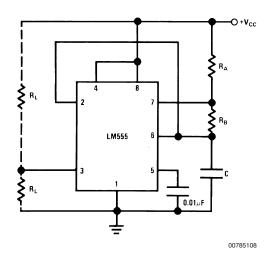

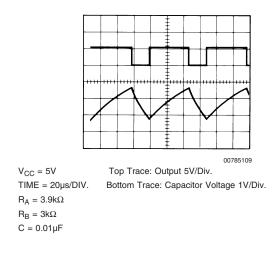

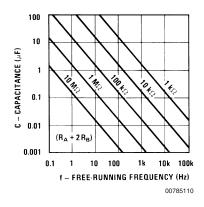

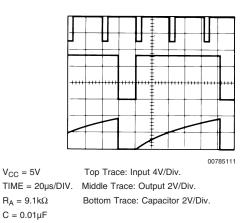

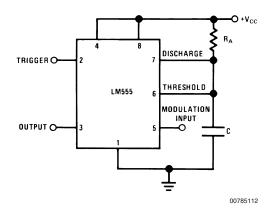

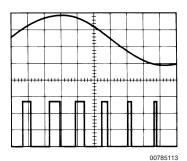

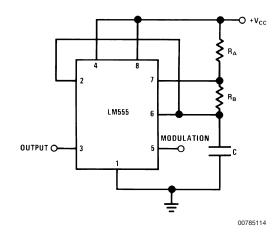

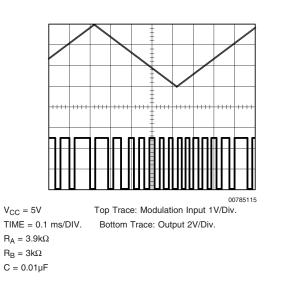

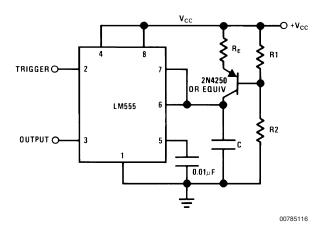

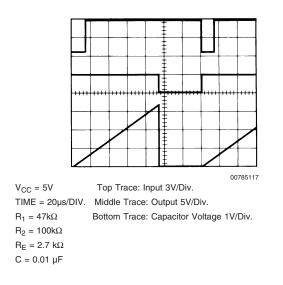

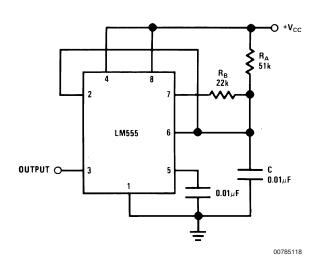

Όσον αφορά τον χρονιστή 555, υλικό προς μελέτη υπάρχει στης παρακάτω ιστοσελίδες:

http://en.wikipedia.org/wiki/555\_timer\_IC http://www.doctronics.co.uk/555.htm

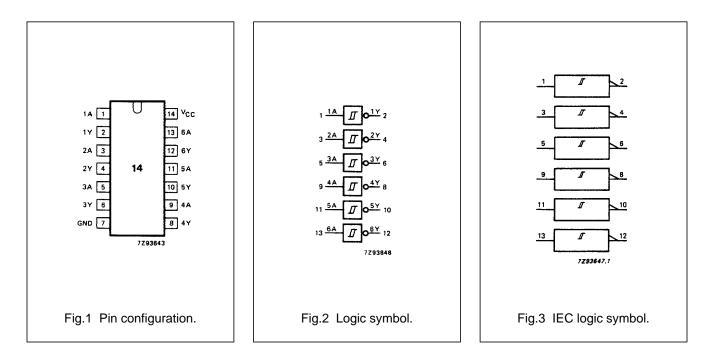

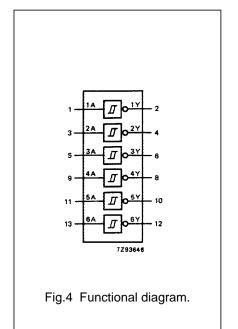

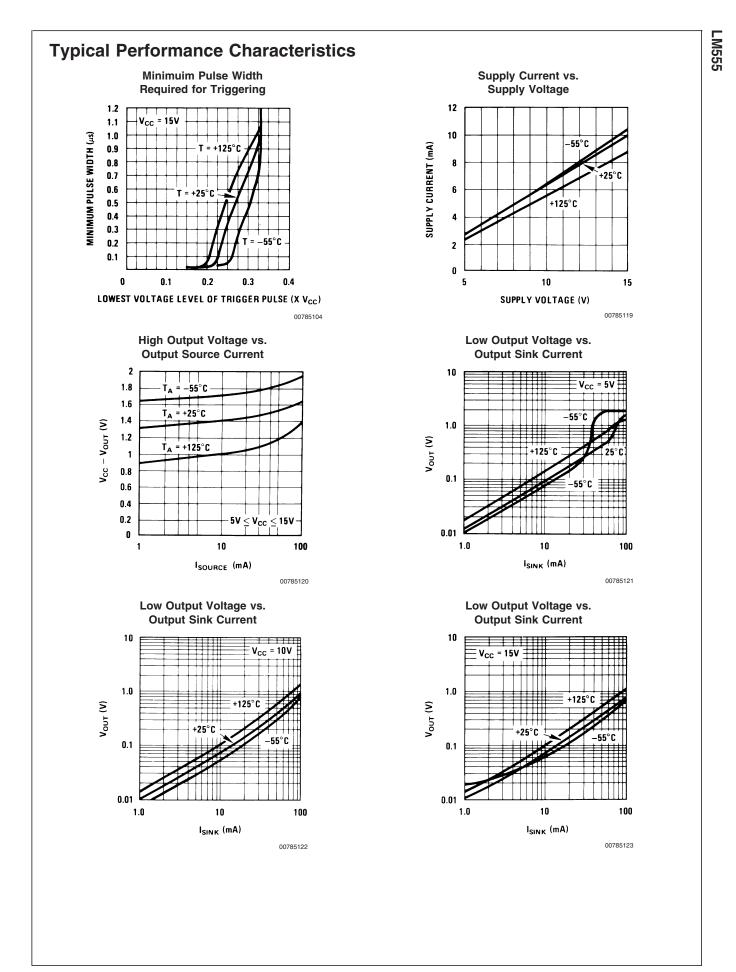

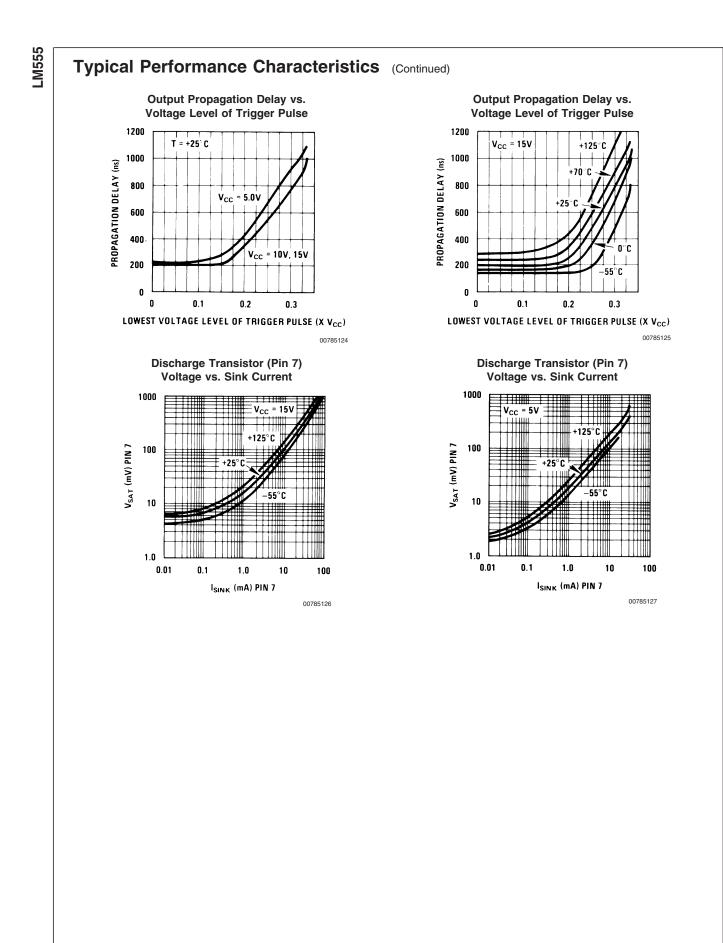

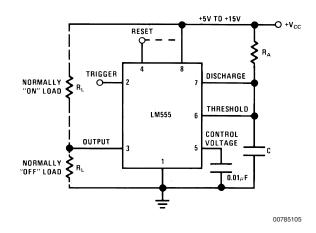

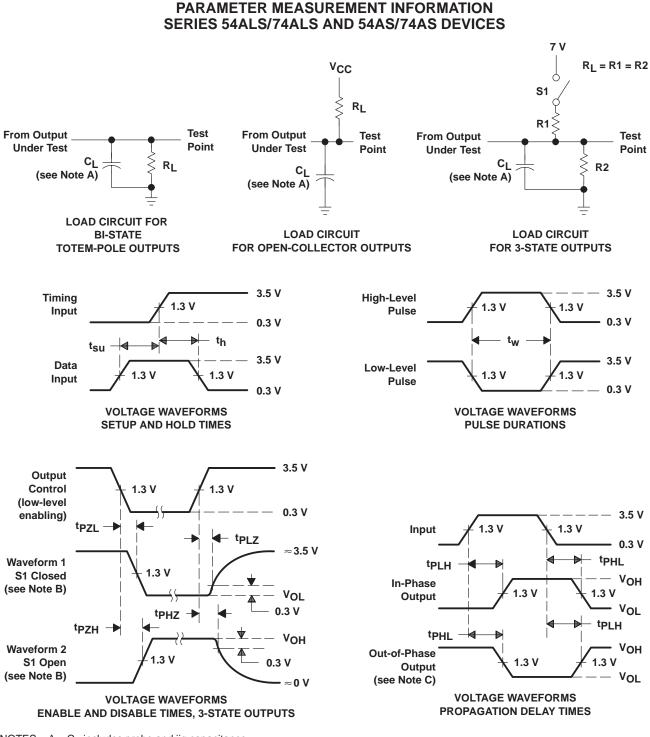

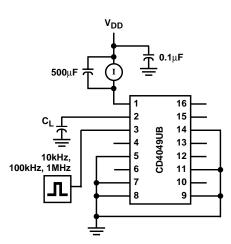

Προφανώς μπορείτε να χρησιμοποιήσετε και συγγράμματα που έχετε πάρει από την σχολή και καλύπτουν τα παραπάνω θεματικά αντικείμενα. Θα χρειαστεί επίσης να μελετήσατε τα datasheets των ολοκληρωμένων 74HC14, LM555, 7400, 74LS00, 74AS00, 74ALS00, 74HC00, 74AC00, 74LS04, CD4007, CD4001B και CD4050B, που χρησιμοποιούνται στα πλαίσια της άσκησης.

#### 4. Εκπαιδευτικό Λογισμικό Εξομοίωσης Εργαστηριακών Ασκήσεων

Στα πλαίσια του εργαστηρίου θα δοθούν οδηγίες για την χρήσης εκπαιδευτικού λογισμικού για την εξομοίωση των εργαστηριακών ασκήσεων σε υπολογιστή κατ' οίκον. Αυτό θα μπορείτε να το χρησιμοποιείτε τόσο στο σπίτι για εξάσκηση, καθώς επίσης και για την περίπτωση όπου στα πλαίσια του εργαστηρίου κάποιοι από εσάς δεν προλάβουν να εκτελέσουν όλες της πειραματικές διατάξεις και να πάρουν όλες της μετρήσεις. Ο τρόπος αξιοποίησης αυτής της πρακτικής θα αναφερθεί στο εργαστήριο ώστε να εξασφαλιστεί ότι δεν θα υπάρχει περίπτωση όπου μια ομάδα θα πάρει απλά τα κυκλώματα και της μετρήσεις από κάποια άλλη ομάδα.

Το εκπαιδευτικό λογισμικό που συνίσταται αν χρησιμοποιήσετε είναι το "PSpice 9.1 Student Version", για το οποίο πιο κάτω θα αναφερθεί πιο συγκεκριμένο στοιχείο θα πρέπει να χρησιμοποιείται για κάθε ένα από τα ολοκληρωμένα κυκλώματα που χρησιμοποιούνται στα πλαίσια των εργαστηριακών ασκήσεων.

To "PSpice 9.1 Student Version", μπορείτε να το κατεβάσετε από κάποια από τα δύο ακόλουθα links:

http://www.electronics-lab.com/downloads/schematic/013/ http://www.electronics-lab.com/downloads/cnt/fclick.php?fid=513

Για την χρήση του "PSpice 9.1 Student Version", θα βρείτε έναν τεράστιο όγκο πληροφοριών στο διαδίκτυο. Κατόπιν αναζήτησης στο διαδίκτυο, βρήκαμε ότι υπάρχει εξαιρετικό ελληνικό εκπαιδευτικό υλικό διαφόρων συναδέλφων που θα σας βοηθήσουν να μάθετε εύκολα και γρήγορα το εν λόγω εργαλείο. Αυτό το εκπαιδευτικό υλικό βρίσκεται στης ακόλουθες ιστοσελίδες:

http://www.ellab.physics.upatras.gr/content/view/162/2/lang.greek/ http://vergina.eng.auth.gr/kontoleon/Page-SPE.htm http://vergina.eng.auth.gr/kontoleon/Page-SPD.htm

Παράλληλα στην προσωπική ιστοσελίδα του διδάσκοντα Χ. Μιχαήλ, υπάρχει οπτικοακουστικό υλικό (video-tutorials) για τον τρόπο χρήσης του συγκεκριμένου εργαλείου σε κυκλώματα vlsi. Ο τρόπος λειτουργίας του εργαλείου είναι ίδιος και απλά εσείς θα πρέπει να επιλέγετε τα κατάλληλα εξαρτήματα για τα κυκλώματα σας.

http://www.vlsi.ece.upatras.gr/~michail/vlsi/vlsi2.htm

Επίσης πολύ κατατοπιστικά, είναι και το ακόλουθα δύο εισαγωγικά κείμενα στην χρήση του "PSpice 9.1 Student Version".

www.ee.sharif.ir/~zandi/**PSpice\_**Handbook.pdf http://userweb.elec.gla.ac.uk/j/jdavies/orcad/spiceintro.pdf http://denethor.wlu.ca/PSpice/pspice\_tutorial.html#HI Επιπλέον εκπαιδευτικό υλικό για την χρήση του "PSpice 9.1 Student Version", μπορείτε να βρείτε και στης ακόλουθες ιστοσελίδες, της οποίες ελέγξαμε και το υπάρχον υλικό είναι πολύ υψηλού επιπέδου:

<u>http://www.ee.nmt.edu/~rison/ee321\_fall02/Tutorial.html</u> <u>http://cobweb.ecn.purdue.edu/~ee255/lecturesupp\_files/PSpice-Tutorial.pdf</u> <u>http://www.engr.colostate.edu/ECE562/Pspicetutorial.pdf</u> <u>http://www.uta.edu/ee/hw/pspice/</u> http://ewh.ieee.org/soc/es/Nov1999/02/BEGIN.HTM

Πιο κάτω θα βρείτε της αντιστοιχίες μεταξύ των στοιχείων κάθε εργαστηριακής άσκησης και του αντίστοιχου στοιχείου που θα πρέπει να χρησιμοποιηθεί από τα διαθέσιμα στο "PSpice 9.1 Student Version", ώστε να μπορείτε εύκολα και γρήγορα να υλοποιείστε τα απαιτούμενα κυκλώματα.

#### ΑΣΚΗΣΗ 1

| ΟΛΟΚΛΗΡΩΜΕΝΟ ΕΡΓΑΣΤΗΡΙΟΥ | ΜΟΝΤΕΛΟ ΤΟΥ SPICE |

|--------------------------|-------------------|

| OPAMP LF411              | LF411             |

| OPAMP LM 741CN           | uA741             |

| Ροοστάτης                | R_var             |

#### ΑΣΚΗΣΗ 2

| ΟΛΟΚΛΗΡΩΜΕΝΟ ΕΡΓΑΣΤΗΡΙΟΥ | ΜΟΝΤΕΛΟ ΤΟΥ SPICE              |

|--------------------------|--------------------------------|

| SN74LS00                 | 7400                           |

| SN74HC00                 | 7400                           |

| D1N4148                  | D1N4148                        |

| CD4007                   | Χρησιμοποιήσατε τα MOSFET      |

|                          | τρανζίστορς MbreakN3D και      |

|                          | MbreakP3D για να οργανώσετε τη |

|                          | συνδεσμολογία που απαιτείται   |

#### ΑΣΚΗΣΗ 3

| ΟΛΟΚΛΗΡΩΜΕΝΟ ΕΡΓΑΣΤΗΡΙΟΥ | ΜΟΝΤΕΛΟ ΤΟΥ SPICE |

|--------------------------|-------------------|

| SN74HC00                 | 7400              |

| SN74HC74                 | 7474              |

| SN74LS112                | 74111             |

| SN74HC08                 | 7408              |

| SN74HC175                | 74175             |

#### ΑΣΚΗΣΗ 4

| ΟΛΟΚΛΗΡΩΜΕΝΟ ΕΡΓΑΣΤΗΡΙΟΥ | ΜΟΝΤΕΛΟ ΤΟΥ SPICE |

|--------------------------|-------------------|

| SN74LS00                 | 7400              |

| SN74HC00                 | 7400              |

| D1N4148                  | D1N4148           |

| SN74HC08                 | 7408              |

| SN74LS04                 | 7404              |

| SN74HC04                 | 7404              |

| CD4050B                  | 7433 ή 7402       |

#### ΑΣΚΗΣΗ 5

| ΟΛΟΚΛΗΡΩΜΕΝΟ ΕΡΓΑΣΤΗΡΙΟΥ | ΜΟΝΤΕΛΟ ΤΟΥ SPICE              |

|--------------------------|--------------------------------|

| SN74HC00                 | 7400                           |

| SN74HC14                 | 7414                           |

| Zener Diode              | DIN750 H 1N4370A               |

| LM555                    | 555D                           |

| SN74LS00                 | 7400                           |

| SN74HC00                 | 7400                           |

| CD4050B                  | 7433 ή 7402                    |

| CD4001B                  | 7433 ή 7402                    |

| CD4007                   | Χρησιμοποιήσατε τα MOSFET      |

|                          | τρανζίστορς MbreakN3D και      |

|                          | MbreakP3D για να οργανώσετε τη |

|                          | συνδεσμολογία που απαιτείται   |

Κατόπιν όλων αυτών που έχουν αναφερθεί πιο πάνω θεωρούμε ότι πλέον έχετε όλα τα απαραίτητα εφόδια, ανεξαρτήτως των μαθημάτων προηγούμενων εξαμήνων που έχετε ή δεν έχετε διαβάσει, ώστε να εκτελέσετε σωστά της εργαστηριακές ασκήσεις κατανοώντας και το αντίστοιχο θεωρητικό υπόβαθρο.

Σας ευχόμαστε καλή επιτυχία...

Οι Διδάσκοντες

Δρ. Χαράλαμπος Μιχαήλ Δρ. Φώτιος Γκιουλέκας

# ΠΑΡΑΡΤΗΜΑΤΑ ΜΕΛΕΤΗΣ ΕΡΓΑΣΤΗΡΙΟΥ ΗΛΕΚΤΡΟΝΙΚΗΣ ΙΙ

# **Operational amplifier**

From Wikipedia, the free encyclopedia

An **operational amplifier**, which is often called an **op-amp**, is a DC-coupled high-gain electronic voltage amplifier with a differential input and, usually, a single-ended output.<sup>[1]</sup> An op-amp produces an output voltage that is typically millions of times larger than the voltage *difference* between its input terminals.

Typically the op-amp's very large gain is controlled by negative feedback, which largely determines the magnitude of its output ("closed-loop") voltage gain in amplifier applications, or the transfer function required (in analog computers). Without negative feedback, and perhaps with positive feedback for

Various op-amp ICs in eight-pin dual in-line packages ("DIPs")

regeneration, an op-amp essentially acts as a comparator. High input impedance at the input terminals (ideally infinite) and low output impedance at the output terminal(s) (ideally zero) are important typical characteristics.

Op-amps are among the most widely used electronic devices today, being used in a vast array of consumer, industrial, and scientific devices. Many standard IC op-amps cost only a few cents in moderate production volume; however some integrated or hybrid operational amplifiers with special performance specifications may cost over \$100 US in small quantities. Op-amps sometimes come in the form of macroscopic components, (see photo) or as integrated circuit cells; patterns that can be reprinted several times on one chip as part of a more complex device.

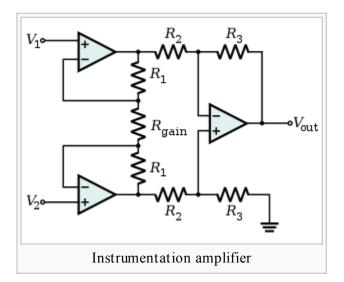

The op-amp is one type of differential amplifier. Other types of differential amplifier include the fully differential amplifier (similar to the op-amp, but with two outputs), the instrumentation amplifier (usually built from three op-amps), the isolation amplifier (similar to the instrumentation amplifier, but which works fine with common-mode voltages that would destroy an ordinary op-amp), and negative feedback amplifier (usually built from one or more op-amps and a resistive feedback network).

# Contents

- 1 Circuit notation

- 2 Operation

- 2.1 Golden rules of op-amp negative feedback

- 2.2 Real and Ideal op-amps

- 3 History

- 3.1 1941: First (vacuum tube) op-amp

- 3.2 1947: First op-amp with an explicit non-inverting input

- 3.3 1949: First chopper-stabilized op-amp

- 3.4 1961: First discrete IC op-amps

- 3.5 1962: First op-amps in potted modules

- 3.6 1963: First monolithic IC op-amp

- 3.7 1968: Release of the µA741 would be seen as a nearly ubiquitous chip

- 3.8 1966: First varactor bridge op-amps

- 3.9 1970: First high-speed, low-input current FET design

- 3.10 1972: Single sided supply op-amps being produced

- 3.11 Recent trends

- 4 Classification of Operational Amplifiers

- 5 Applications

- 5.1 Use in electronics system design

- 5.2 Positive feedback configurations

- 5.3 Basic single stage amplifiers

- 5.3.1 Non-inverting amplifier

- 5.3.2 Inverting amplifier

- 5.4 Other applications

- 6 Limitations of real op-amps

- 6.1 DC imperfections

- 6.2 AC imperfections

- 6.3 Nonlinear imperfections

- 6.4 Power considerations

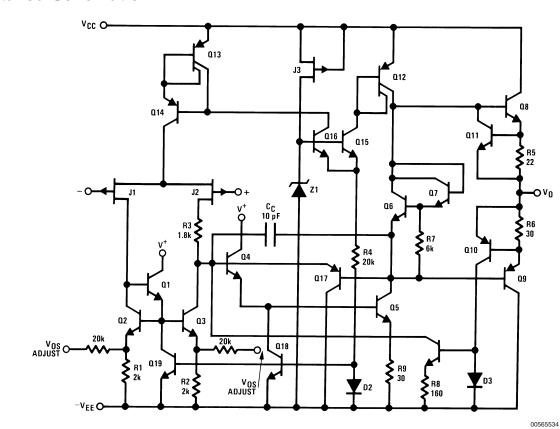

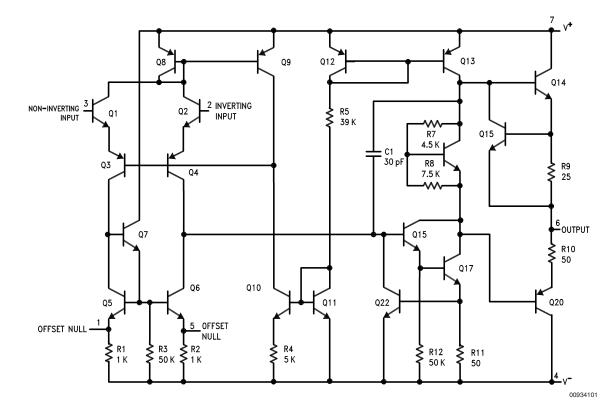

- 7 Internal circuitry of 741 type op-amp

- 7.1 Input stage

- 7.1.1 Constant-current stabilization system

- 7.1.2 Differential amplifier

- 7.2 Class A gain stage

- 7.3 Output bias circuitry

- 7.4 Output stage

- 8 See also

- 9 Notes

- 10 References

- 11 External links

# **Circuit notation**

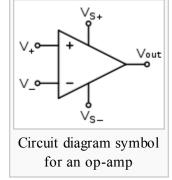

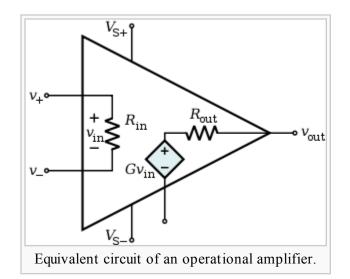

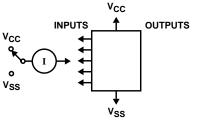

The circuit symbol for an op-amp is shown to the right, where:

- $V_+$ : non-inverting input

- V\_: inverting input

- Vout: output

- $V_{S+}$ : positive power supply

- V<sub>S</sub>\_: negative power supply

The power supply pins ( $V_{S+}$  and  $V_{S-}$ ) can be labeled in different ways (*See IC* power supply pins). Despite different labeling, the function remains the same — to provide additional power for amplification of signal. Often these pins are left out of the diagram for clarity, and the power configuration is described or assumed from the circuit.

# Operation

The amplifier's differential inputs consist of a  $V_+$  input and a  $V_-$  input, and ideally the op-amp amplifies only the difference in voltage between the two, which is called the *differential input voltage*. The output voltage of the op-amp is given by the equation,

$$V_{\text{out}} = (V_+ - V_-) G_{\text{open-loop}}$$

where  $V_+$  is the voltage at the non-inverting terminal,  $V_-$  is the voltage at the inverting terminal and  $G_{\text{open-loop}}$  is the open-loop gain of the amplifier. (The term open-loop refers to the absence of a feedback loop from the output to the input.)

The magnitude of  $G_{\text{open-loop}}$  is typically very large—seldom less than a million—and therefore even a quite small difference between  $V_+$  and  $V_-$  (a few microvolts or less) will result in amplifier saturation, where the output voltage goes to either the extreme maximum or minimum end of its range, which is set approximately by the power supply voltages. *Finley's law* states that "When the inverting and non-inverting inputs of an op-amp are not equal, its output is in saturation." Additionally, the precise magnitude of

$G_{\text{open-loop}}$  is not well controlled by the manufacturing process,

and so it is impractical to use an operational amplifier as a stand-alone differential amplifier. If linear operation is desired, negative feedback must be used, usually achieved by applying a portion of the output voltage to the inverting input. The feedback enables the output of the amplifier to keep the inputs at or near the same voltage so that saturation does not occur. Another benefit is that if much negative feedback is used, the circuit's overall gain and other parameters become determined more by the feedback network than by the op-amp itself. If the feedback network is made of components with relatively constant, predictable, values such as resistors, capacitors and inductors, the unpredictability and inconstancy of the op-amp's parameters (typical of semiconductor devices) do not seriously affect the circuit's performance.

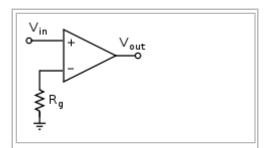

With no negative feedback, the op-amp acts as a switch. The inverting input is held at ground (0 V) by the resistor, so if the  $V_{in}$  applied to the non-inverting input is positive, the output will be maximum positive, and if  $V_{in}$  is negative, the output will be maximum negative. Since there is no feedback from the output to either input, this is an *open loop* circuit. The circuit's gain is just the G<sub>open-loop</sub> of the op-amp.

If no negative feedback is used, the op-amp functions as a switch or comparator.

Positive feedback may be used to introduce hysteresis or oscillation.

Returning to a consideration of linear (negative feedback) operation, the high open-loop gain and low input leakage current of the op-amp imply two "golden rules" that are highly useful in analysing linear op-amp circuits.

# Golden rules of op-amp negative feedback

If there is negative feedback and if the output is not saturated,

- 1. both inputs are at the same voltage;

- 2. no current flows in or out of either input.<sup>[2]</sup>

These rules are true of the ideal op-amp and for practical purposes are true of real op-amps unless very high-speed or high-precision performance is being contemplated (in which case account must be taken of things such as input capacitance, input bias currents and voltages, finite speed, and other op-amp imperfections, discussed in a later section.)

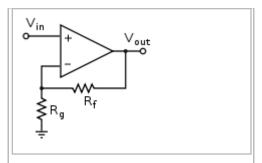

Adding negative feedback via  $R_f$ reduces the gain. Equilibrium will be established when  $V_{out}$  is just sufficient to reach around and pull the inverting input to the same voltage as  $V_{in}$ . As a simple example, if  $V_{in} = 1$  V and  $R_f =$  $R_g$ ,  $V_{out}$  will be 2 V, the amount required to keep  $V_-$  at 1 V. Because of the feedback provided by  $R_f$ , this is a *closed loop* circuit. Its over-all gain  $V_{out} / V_{in}$  is called the *closed-loop gain*  $G_{closed-loop}$ . Because the feedback is negative, in this case  $G_{closed-loop}$  is less than the  $G_{open-loop}$  of the op-amp.

As a consequence of the first rule, the input impedance of the two inputs will be nearly infinite. That is, even if the open-loop impedance between the two inputs is low, the closed-loop input impedance will be high because the inputs will be held at nearly the same voltage. This impedance is considered as infinite for an ideal opamp and is about one megohm in practice.

# Real and Ideal op-amps

Shown on the right is an equivalent circuit model of an operational amplifier. The main part in the amplifier is the dependent voltage source that increases in relation to the voltage across  $R_{\rm in}$ , thus amplifying the voltage difference between  $V_+$  and  $V_-$ .

Supply voltages  $V_{S+}$  and  $V_{S-}$  are used internally to power the dependent voltage source. The positive supply  $V_{S+}$  sets an upper bound on the output, and the negative source  $V_{S-}$ sets a lower bound on the output.

More sophisticated equivalent circuit models can also be constructed which include things such as input capacitance and input bias. On the other hand, one can imagine an even simpler "ideal" op-amp by assuming  $R_{in}$  to be infinite and

$R_{\text{out}} = 0.$

An ideal op-amp is usually considered to have the following properties, and they are considered to hold for any input voltages:

- Infinite open-loop gain (i.e., when doing theoretical analysis, limit should be taken as open loop gain Gopen-loop goes to infinity)

- Infinite bandwidth (i.e., the frequency magnitude response is flat everywhere with zero phase shift).

- Infinite input impedance (so, in the diagram,  $R_{\rm in}=\infty$ , and zero current flows from  $V_+$  to  $V_-$  )

- Zero input current (i.e., there is no leakage or bias current into the device)

- Zero input offset voltage (i.e., when the input terminals are shorted so that V<sub>+</sub> = V<sub>-</sub>, the output is a virtual ground).

- Infinite slew rate (i.e., the rate of change of the output voltage is unbounded) and power bandwidth (full output voltage and current available at all frequencies).

- Zero output impedance (i.e.,  $R_{out} = 0$ , and so output voltage does not vary with output current)

- Zero noise

- Infinite Common-mode rejection ratio (CMRR)

- Infinite Power supply rejection ratio for both power supply rails.

Because of these properties, an op-amp can be modeled as a nullor.

# History

## 1941: First (vacuum tube) op-amp

An op-amp, defined as a general-purpose, DC-coupled, high gain, inverting feedback amplifier, is first found in US Patent 2,401,779 "Summing Amplifier" filed by Karl D. Swartzel Jr. of Bell labs in 1941. This design used three vacuum tubes to achieve a gain of 90dB and operated on voltage rails of  $\pm 350$ V. It had a single inverting input rather than differential inverting and non-inverting inputs, as are common in today's op-amps. Throughout World War II, Swartzel's design proved its value by being liberally used in the M9 artillery director designed at Bell Labs. This artillery director worked with the SCR584 radar system to achieve extraordinary hit rates (near 90%) that would not have been possible otherwise.<sup>[3]</sup>

# **1947:** First op-amp with an explicit non-inverting input

ADI's HOS-050: a high speed hybrid IC op-amp (1979).

An op-amp in a modern DIP.

In 1947, the operational amplifier was first formally defined and named in a paper by Professor John R. Ragazzini of Columbia University. In this same paper a footnote mentioned an op-amp design by a student that would turn out to be quite significant.

This op-amp, designed by Loebe Julie, was superior in a variety of ways. It had two major innovations. Its input stage used a long-tailed triode pair with loads matched to reduce drift in the output and, far more importantly, it was the first op-amp design to have two inputs (one inverting, the other non-inverting). The differential input made a whole range of new functionality possible, but it would not be used for a long time due

to the rise of the chopper-stabilized amplifier.<sup>[4]</sup>

# 1949: First chopper-stabilized op-amp

In 1949, Edwin A. Goldberg designed a chopper-stabilized op-amp.<sup>[5]</sup> This set-up uses a normal op-amp with an additional AC amplifier that goes alongside the op-amp. The chopper gets an AC signal from DC by switching between the DC voltage and ground at a fast rate (60 Hz or 400 Hz). This signal is then amplified, rectified, filtered and fed into the op-amp's non-inverting input. This vastly improved the gain of the op-amp while significantly reducing the output drift and DC offset. Unfortunately, any design that used a chopper couldn't use their non-inverting input for any other purpose. Nevertheless, the much improved characteristics of the chopper-stabilized op-amp made it the dominant way to use op-amps. Techniques that used the non-inverting input regularly would not be very popular until the 1960s when op-amp ICs started to show up in the field.

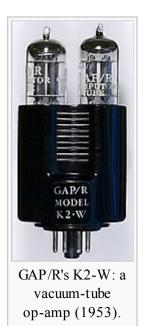

In 1953, vacuum tube op-amps became commercially available with the release of the model K2-W from George A. Philbrick Researches, Incorporated. The designation on the devices shown, GAP/R, is a contraction for the complete company name. Two nine-pin 12AX7 vacuum tubes were mounted in an octal package and had a model K2-P chopper add-on available that would effectively "use up" the non-inverting input. This op-amp was based on a descendant of Loebe Julie's 1947 design and, along with its successors, would start the widespread use of op-amps in industry.

## 1961: First discrete IC op-amps

GAP/R's model P45: a solid-state, discrete op-amp (1961).

With the birth of the transistor in 1947, and the silicon transistor in 1954, the concept of ICs became a reality. The introduction of the planar process in 1959 made transistors and ICs stable enough to be commercially useful. By 1961, solid-state, discrete op-amps were being produced. These op-amps were effectively small circuit boards with packages such as edge-connectors. They usually had hand-selected resistors in order to improve things such as voltage offset and drift. The P45 (1961) had a gain of 94 dB and ran on  $\pm 15$  V rails. It was intended to deal with signals in the range of  $\pm 10$  V.

## 1962: First op-amps in potted modules

By 1962, several companies were producing modular potted packages that could be plugged into printed circuit boards.<sup>[citation needed]</sup> These packages were crucially important as they made the operational amplifier into a single black box which could be easily treated as a component in a larger circuit.

# 1963: First monolithic IC op-amp

In 1963, the first monolithic IC op-amp, the  $\mu$ A702 designed by Bob Widlar at Fairchild Semiconductor, was released. Monolithic ICs consist of a single chip as opposed to a chip and discrete parts (a discrete IC) or multiple chips bonded and connected on a circuit board (a hybrid IC). Almost all modern op-amps are monolithic ICs; however, this first IC did not meet with much success. Issues such as an uneven supply voltage, low gain and a small dynamic range held off the dominance of monolithic op-amps until 1965 when the  $\mu$ A709<sup>[6]</sup> (also designed by Bob Widlar) was released.

GAP/R's model PP65: a solid-state op-amp in a potted module (1962).

# 1968: Release of the µA741 – would be seen as a nearly ubiquitous chip

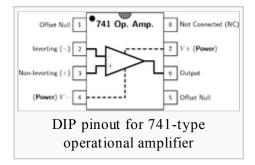

The popularity of monolithic op-amps was further improved upon the release of the LM101 in 1967, which solved a variety of issues, and the subsequent release of the  $\mu$ A741 in 1968. The  $\mu$ A741 was extremely similar to the LM101 except that Fairchild's facilities allowed them to include a 30 pF compensation capacitor inside the chip instead of requiring external compensation. This simple difference has made the 741 *the* canonical op-amp and many modern amps base their pinout on the 741s. The  $\mu$ A741 is still in production, and has become ubiquitous in electronics—many manufacturers produce a version of this classic chip, recognizable by part numbers containing 741.

### 1966: First varactor bridge op-amps

Since the 741, there have been many different directions taken in op-amp design. Varactor bridge op-amps started to be produced in the late 1960s; they were designed to have extremely small input current and are still amongst the best op-amps available in terms of common-mode rejection with the ability to correctly deal with hundreds of volts at their inputs.

## 1970: First high-speed, low-input current FET design

In the 1970s high speed, low-input current designs started to be made by using FETs. These would be largely replaced by op-amps made with MOSFETs in the 1980s. During the 1970s single sided supply op-amps also became available.

## 1972: Single sided supply op-amps being produced

A single sided supply op-amp is one where the input and output voltages can be as low as the negative power supply voltage instead of needing to be at least two volts above it. The result is that it can operate in many applications with the negative supply pin on the op-amp being connected to the signal ground, thus eliminating the need for a separate negative power supply.

The LM 324 (released in 1972) was one such op-amp that came in a quad package (four separate op-amps in one package) and became an industry standard. In addition to packaging multiple op-amps in a single package, the 1970s also saw the birth of op-amps in hybrid packages. These op-amps were generally improved versions of existing monolithic op-amps. As the properties of monolithic op-amps improved, the more complex hybrid ICs were quickly relegated to systems that are required to have extremely long service lives or other specialty systems.

## **Recent trends**

Recently supply voltages in analog circuits have decreased (as they have in digital logic) and low-voltage opamps have been introduced reflecting this. Supplies of  $\pm 5V$  and increasingly 5V are common. To maximize the signal range modern op-amps commonly have rail-to-rail inputs (the input signals can range from the lowest supply voltage to the highest) and sometimes rail-to-rail outputs.

# **Classification of Operational Amplifiers**

Op-amps may be classified by their construction:

- discrete (built from individual transistors or tubes/valves)

- IC (fabricated in an Integrated circuit) most common

- hybrid

IC op-amps may be classified in many ways, including:

- Military, Industrial, or Commercial grade (for example: the LM 301 is the commercial grade version of the LM 101, the LM 201 is the industrial version). This may define operating temperature ranges and other environmental or quality factors.

- Classification by package type may also affect environmental hardiness, as well as manufacturing options; DIP, and other through-hole packages are tending to be replaced by Surface-mount devices.

- Classification by internal compensation: op-amps may suffer from high frequency instability in some negative feedback circuits unless a small compensation capacitor modifies the phase- and frequency-responses; op-amps with capacitor built in are termed **compensated**, or perhaps compensated for closed-loop gains down to (say) 5, others: uncompensated.

- Single, dual and quad versions of many commercial op-amp IC are available, meaning 1, 2 or 4 operational amplifiers are included in the same package.

- Rail-to-rail input (and/or output) op-amps can work with input (and/or output) signals very close to the power supply rails.

- CMOS op-amps (such as the CA3140E) provide extremely high input resistances, higher than JFET-input op-amps, which are normally higher than bipolar-input op-amps.

- other varieties of op-amp include programmable op-amps (simply meaning the quiescent current, gain, bandwidth and so on can be adjusted slightly by an external resistor).

- manufacturers often tabulate their op-amps according to purpose, such as low-noise pre-amplifiers, wide bandwidth amplifiers, and so on.

# Applications

Main article: Operational amplifier applications

## Use in electronics system design

The use of op-amps as circuit blocks is much easier and clearer than specifying all their individual circuit elements (transistors, resistors, etc.), whether the amplifiers used are integrated or discrete. In the first approximation op-amps can be used as if they were ideal differential gain blocks; at a later stage limits can be placed on the acceptable range of parameters for each op-amp.

Circuit design follows the same lines for all electronic circuits. A specification is drawn up governing what the circuit is required to do, with allowable limits. For example, the gain may be required to be 100 times, with a tolerance of 5% but drift of less than 1% in a specified temperature range; the input impedance not less than one megohm; etc.

A basic circuit is designed, often with the help of circuit modeling (on a computer). Specific commercially available op-amps and other components are then chosen that meet the design criteria within the specified tolerances at acceptable cost. If not all criteria can be met, the specification may need to be modified.

A prototype is then built and tested; changes to meet or improve the specification, alter functionality, or reduce the cost, may be made.

## Positive feedback configurations

Another typical configuration of op-amps is the positive feedback, which takes a fraction of the output signal back to the non-inverting input. An important application of it is the comparator with hysteresis (i.e., the Schmitt trigger).

### **Basic single stage amplifiers**

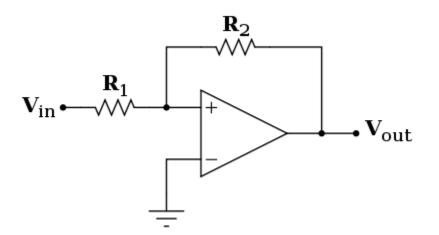

#### Non-inverting amplifier

The gain equation for the op-amp is:

$$V_{\text{out}} = (V_+ - V_-) G_{\text{open-loop}}$$

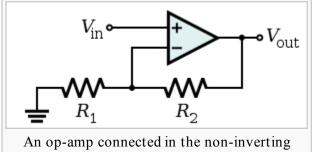

However, in this circuit  $V_{-}$  is a function of  $V_{out}$  because of the negative feedback through the  $R_1R_2$  network.  $R_1$  and  $R_2$  form a voltage divider with reduction factor

$$F = \frac{R_1}{R_1 + R_2}$$

amplifier configuration

Since the  $V_{-}$  input is a high-impedance input, it does not load the voltage divider appreciably, so:

$$V_{-} = F \cdot V_{\text{out}}$$

Substituting this into the gain equation, we obtain:

$$V_{\text{out}} = (V_{\text{in}} - F \cdot V_{\text{out}}) \cdot G_{\text{open-loop}}$$

Solving for  $V_{out}$ :

$$V_{\rm out} = V_{\rm in} \cdot \left(\frac{1}{F + 1/G_{\rm open-loop}}\right)$$

If  $G_{\text{open-loop}}$  is very large, this simplifies to

$$V_{out} = \frac{V_{in}}{F} = V_{in} / \frac{R_1}{R_1 + R_2} = V_{in} (1 + \frac{R_2}{R_1}).$$

Inverting amplifier

Because it does not require a differential input, this negative feedback connection was the most typical use of an op-amp in the days of analog computers.<sup>[citation needed]</sup> It remains very popular.<sup>[citation needed]</sup>

This circuit is easily analysed with the help of the two "golden rules".

Since the non-inverting input is grounded, rule 1 tells us that the inverting input will also be at ground potential (0 Volts):

$$V_{-} \approx V_{+-} = 0$$

The current through  $R_{in}$  is then:

$$I_{in} = V_{in}/R_{in}$$

Rule 2 tells us that no current enters the inverting input.

Then, by Kirchoff's current law the current through  $R_{f}$  must be the same as the current through  $R_{in}$ . The voltage drop across  $R_{f}$  is then given by Ohm's law:

$$V_{\rm Rf} = R_{\rm f} \cdot I_{\rm in} = V_{\rm in} \frac{R_{\rm f}}{R_{\rm in}}$$

Since  $V_{-}$  is zero volts,  $V_{out}$  is just  $-V_{Rf}$ .

$$V_{\rm out} = -V_{\rm in} \frac{R_{\rm f}}{R_{\rm in}}$$

[7]

- Some Variations:

- A resistor is often inserted between the non-inverting input and ground (so both inputs "see" similar resistances), reducing the input offset voltage due to different voltage drops due to bias current, and may reduce distortion in some op-amps.

- A DC-blocking capacitor may be inserted in series with the input resistor when a frequency response down to DC is not needed and any DC voltage on the input is unwanted. That is, the capacitive component of the input impedance inserts a DC zero and a low-frequency pole that gives the circuit a bandpass or high-pass characteristic.

## **Other applications**

- audio- and video-frequency pre-amplifiers and buffers

- voltage comparators

- differential amplifiers

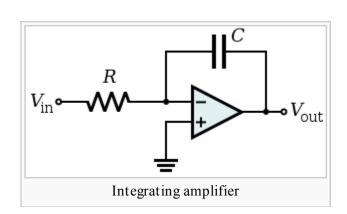

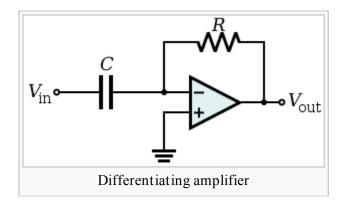

- differentiators and integrators

- filters

- precision rectifiers

amplifier configuration

- precision peak detectors

- voltage and current regulators

- analog calculators

- analog-to-digital converters

- digital-to-analog converter

- voltage clamps

- oscillators and waveform generators

Most single, dual and quad op-amps available have a standardized pin-out which permits one type to be substituted for another without wiring changes. A specific op-amp may be chosen for its open loop gain, bandwidth, noise performance, input impedance, power consumption, or a compromise between any of these factors.

# Limitations of real op-amps

Real op-amps differ from the ideal model in various respects.

IC op-amps as implemented in practice are moderately complex integrated circuits; see the internal circuitry for the relatively simple 741 op-amp below, for example.

## **DC** imperfections

Real operational amplifiers suffer from several non-ideal effects:

Finite gain

Open-loop gain is infinite in the ideal operational amplifier but finite in real operational amplifiers. Typical devices exhibit open-loop DC gain ranging from 100,000 to over 1 million. So long as the loop gain (i.e., the product of open-loop and feedback gains) is very large, the circuit gain will be determined entirely by the amount of negative feedback (i.e., it will be independent of open-loop gain). In cases where closed-loop gain must be very high, the feedback gain will be very low, and the low feedback gain causes low loop gain; in these cases, the operational amplifier will cease to behave ideally.

Finite input impedance

The input impedance of the operational amplifier is defined as the impedance *between* its two inputs. It is *not* the impedance from each input to ground. In the typical high-gain negative-feedback applications, the feedback ensures that the two inputs sit at the same voltage, and so the impedance between them is made artificially very high. Hence, this parameter is rarely an important design parameter. Because MOSFET-input operational amplifiers often have protection circuits that effectively short circuit any input differences greater than a small threshold, the input impedance can appear to be very low in some tests. However, as long as these operational amplifiers are used in a typical high-gain negative feedback application, these protection circuits will be inactive and the negative feedback will render the input impedance to be practically infinite. The input bias and leakage currents described below are a more important design parameter for typical operational amplifier applications.

Non-zero output impedance

Low output impedance is important for low resistance loads; for these loads, the voltage drop across the output impedance of the amplifier will be significant. Hence, the output impedance of the amplifier reflects the maximum power that can be provided. If the output voltage is fed back negatively, the output

impedance of the amplifier is effectively lowered; thus, in linear applications, op-amps usually exhibit a very low output impedance indeed. Negative feedback can not, however, reduce the limitations that  $R_{load}$  in conjunction with  $R_{out}$  place on the maximum and minimum possible output voltages; it can only reduce output errors *within* that range.

Low-impedance outputs typically require high quiescent (i.e., idle) current in the output stage and will dissipate more power. So low-power designs may purposely sacrifice low-impedance outputs.

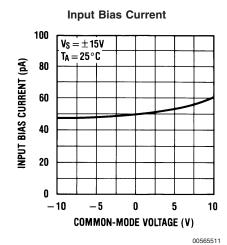

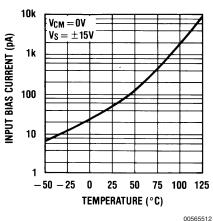

#### Input current

Due to biasing requirements or leakage, a small amount of current (typically ~10 nanoamperes for bipolar op-amps, tens of picoamperes for JFET input stages, and only a few pA for MOSFET input stages) flows into the inputs. When large resistors or sources with high output impedances are used in the circuit, these small currents can produce large unmodeled voltage drops. If the input currents are **matched** *and* the impedance looking *out* of *both* inputs are **matched**, then the voltages produced at each input will be equal. Because the operational amplifier operates on the *difference* between its inputs, these matched voltages will have no effect (unless the operational amplifier has poor CMRR, which is described below). It is more common for the input currents (or the impedances looking out of each input) to be slightly mismatched, and so a small **offset voltage** can be produced. This offset voltage can create offsets or drifting in the operational amplifier. It can often be nulled externally; however, many operational amplifiers include *offset null* or *balance* pins and some procedure for using them to remove this offset. Some operational amplifiers attempt to nullify this offset automatically.

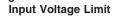

#### Input offset voltage

This voltage, which is what is required across the op-amp's input terminals to drive the output voltage to zero,<sup>[8][nb 1]</sup> is related to the mismatches in input bias current. In the perfect amplifier, there would be no input offset voltage. However, it exists in actual op-amps because of imperfections in the differential amplifier that constitutes the input stage of the vast majority of these devices. Input offset voltage creates two problems: First, due to the amplifier's high voltage gain, it virtually assures that the amplifier output will go into saturation if it is operated without negative feedback, even when the input terminals are wired together. Second, in a closed loop, negative feedback configuration, the input offset voltage is amplified along with the signal and this may pose a problem if high precision DC amplification is required or if the input signal is very small.<sup>[nb 2]</sup>

#### Common mode gain

A perfect operational amplifier amplifies only the voltage difference between its two inputs, completely rejecting all voltages that are common to both. However, the differential input stage of an operational amplifier is never perfect, leading to the amplification of these identical voltages to some degree. The standard measure of this defect is called the common-mode rejection ratio (denoted CMRR). M inimization of common mode gain is usually important in non-inverting amplifiers (described below) that operate at high amplification.

#### Temperature effects

All parameters change with temperature. Temperature drift of the input offset voltage is especially important.

#### Power-supply rejection

The output of a perfect operational amplifier will be completely independent from ripples that arrive on its power supply inputs. Every real operational amplifier has a specified power supply rejection ratio (PSRR) that reflects how well the op-amp can reject changes in its supply voltage. Copious use of bypass

capacitors can improve the PSRR of many devices, including the operational amplifier.

Drift

Real op-amp parameters are subject to slow change over time and with changes in temperature, input conditions, etc.

# **AC** imperfections

The op-amp gain calculated at DC does not apply at higher frequencies. To a first approximation, the gain of a typical op-amp is inversely proportional to frequency. This means that an op-amp is characterized by its gain-bandwidth product. For example, an op-amp with a gain bandwidth product of 1 MHz would have a gain of 5 at 200 kHz, and a gain of 1 at 1 MHz. This low-pass characteristic is introduced deliberately, because it tends to stabilize the circuit by introducing a dominant pole. This is known as frequency compensation.

Typical low cost, general purpose op-amps exhibit a gain bandwidth product of a few megahertz. Specialty and high speed op-amps can achieve gain bandwidth products of hundreds of megahertz. For very high-frequency circuits, a completely different form of op-amp called the current-feedback operational amplifier is often used.

Other imperfections include:

- Finite bandwidth all amplifiers have a finite bandwidth. This creates several problems for op amps. First, associated with the bandwidth limitation is a phase difference between the input signal and the amplifier output that can lead to oscillation in some feedback circuits. The internal frequency compensation used in some op amps to increase the gain or phase margin intentionally reduces the bandwidth even further to maintain output stability when using a wide variety of feedback networks. Second, reduced bandwidth results in lower amounts of feedback at higher frequencies, producing higher distortion, noise, and output impedance and also reduced output phase linearity as the frequency increases.

- Input capacitance most important for high frequency operation because it further reduces the open loop bandwidth of the amplifier.

- Common mode gain See DC imperfections, above.

# Nonlinear imperfections

- Saturation output voltage is limited to a minimum and maximum value close to the power supply voltages.<sup>[nb 3]</sup> Saturation occurs when the output of the amplifier reaches this value and is usually due to:

- In the case of an op-amp using a bipolar power supply, a voltage gain that produces an output that is more positive or more negative than that maximum or minimum; or

- In the case of an op-amp using a single supply voltage, either a voltage gain that produces an output that is more positive than that maximum, or a signal so close to ground that the amplifier's gain is not sufficient to raise it above the lower threshold. [nb 4]

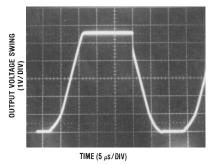

- Slewing the amplifier's output voltage reaches its maximum rate of change. Measured as the slew rate, it is usually specified in volts per microsecond. When slewing occurs, further increases in the input signal have no effect on the rate of change of the output. Slewing is usually caused by internal capacitances in the amplifier, especially those used to implement its frequency compensation.

- Non-linear transfer function The output voltage may not be accurately proportional to the difference between the input voltages. It is commonly called distortion when the input signal is a waveform. This

effect will be very small in a practical circuit if substantial negative feedback is used.

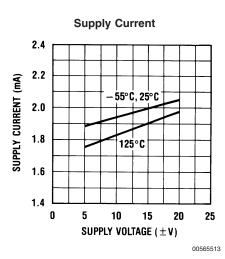

### **Power considerations**

- Limited output current the output current must obviously be finite. In practice, most op-amps are designed to limit the output current so as not to exceed a specified level around 25 mA for a type 741 IC op-amp thus protecting the op-amp and associated circuitry from damage. Modern designs are electronically more rugged than earlier implementations and some can sustain direct short circuits on their outputs without damage.

- Limited dissipated power an op-amp is a linear amplifier. It therefore dissipates some power as heat, proportional to the output current, and to the difference between the output voltage and the supply voltage. If the op-amp dissipates too much power, then its temperature will increase above some safe limit. The op-amp may enter thermal shutdown, or it may be destroyed.

Modern integrated FET or MOSFET op-amps approximate more closely the ideal op-amp than bipolar ICs when it comes to input impedance and input bias and offset currents. Bipolars are generally better when it comes to input *voltage* offset, and often have lower noise. Generally, at room temperature, with a fairly large signal, and limited bandwidth, FET and MOSFET op-amps now offer better performance.

# Internal circuitry of 741 type op-amp

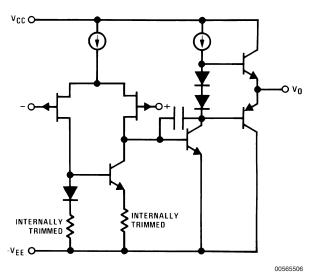

Though designs vary between products and manufacturers, all op-amps have basically the same internal structure, which consists of three stages:

- Differential amplifier provides low noise amplification, high input impedance, usually a differential output.

- Voltage amplifier provides high voltage gain, a single-pole frequency roll-off, usually single-ended output.

- Output amplifier provides high current driving capability, low output impedance, current limiting and short circuit protection circuitry.

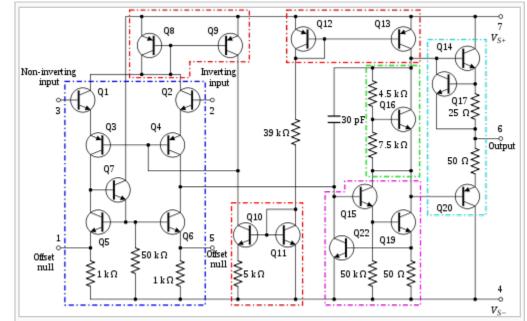

A component level diagram of the common 741 op-amp. Dotted lines outline: current mirrors (red); differential amplifier (blue); class A gain stage (magenta); voltage level shifter (green); output stage (cyan).

## Input stage

#### Constant-current stabilization system

The input stage DC conditions are stabilized by a high-gain negative feedback system whose main parts are the two current mirrors on the left of the figure, outlined in red. The main purpose of this negative feedback system—to supply the differential input stage with a stable constant current—is realized as follows.

The current through the 39 k $\Omega$  resistor acts as a current reference for the other bias currents used in the chip. The voltage across the resistor is equal to the voltage across the supply rails  $(V_{S+} - V_{S-})$  minus two transistor diode drops (i.e., from Q11 and Q12), and so the current has value  $I_{ref} = (V_{S+} - V_{S-} - 2V_{be})/(39 \text{ k}\Omega)$ . The Widlar current mirror built by Q10, Q11, and the 5 k $\Omega$  resistor produces a very small fraction of  $I_{ref}$  at the Q10 collector. This small constant current through Q10's collector supplies the base currents for Q3 and Q4 as well as the Q9 collector current. The Q8/Q9 current mirror tries to make Q9's collector current the same as the Q3 and Q4 *collector* currents. Thus Q3 and Q4's combined base currents (which are of the same order as the overall chip's input currents) will be a small fraction of the already small Q10 current.

So, if the input stage current increases for any reason, the Q8/Q9 current mirror will draw current away from the bases of Q3 and Q4, which reduces the input stage current, and vice versa. The feedback loop also isolates the rest of the circuit from common-mode signals by making the base voltage of Q3/Q4 follow tightly  $2V_{be}$  below the higher of the two input voltages.

#### Differential amplifier

The blue outlined section is a differential amplifier. Q1 and Q2 are input emitter followers and together with the common base pair Q3 and Q4 form the differential input stage. In addition, Q3 and Q4 also act as level shifters and provide voltage gain to drive the class A amplifier. They also help to increase the reverse  $V_{be}$  rating on the input transistors (the emitter-base junctions of the NPN transistors Q1 and Q2 break down at around 7 V but the PNP transistors Q3 and Q4 have breakdown voltages around 50 V)<sup>[9]</sup>.

The differential amplifier formed by Q1–Q4 drives a current mirror active load formed by transistors Q5–Q7 (actually, Q6 is the very active load). Q7 increases the accuracy of the current mirror by decreasing the amount of signal current required from Q3 to drive the bases of Q5 and Q6. This configuration provides differential to single ended conversion as follows:

The signal current of Q3 is the input to the current mirror while the output of the mirror (the collector of Q6) is connected to the collector of Q4. Here, the signal currents of Q3 and Q4 are summed. For differential input signals, the signal currents of Q3 and Q4 are equal and opposite. Thus, the sum is twice the individual signal currents. This completes the differential to single ended conversion.

The open circuit signal voltage appearing at this point is given by the product of the summed signal currents and the paralleled collector resistances of Q4 and Q6. Since the collectors of Q4 and Q6 appear as high resistances to the signal current, the open circuit voltage gain of this stage is very high.

It should be noted that the base current at the inputs is not zero and the effective (differential) input impedance of a 741 is about 2 M $\Omega$ . The "offset null" pins may be used to place external resistors in parallel with the two 1 k $\Omega$  resistors (typically in the form of the two ends of a potentiometer) to adjust the balancing of the Q5/Q6 current mirror and thus indirectly control the output of the op-amp when zero signal is applied between the inputs.

# Class A gain stage

The section outlined in magenta is the class A gain stage. The top-right current mirror Q12/Q13 supplies this stage by a constant current load, via the collector of Q13, that is largely independent of the output voltage. The stage consists of two NPN transistors in a Darlington configuration and uses the output side of a current mirror as its collector load to achieve high gain. The 30 pF capacitor provides frequency selective negative feedback around the class A gain stage as a means of frequency compensation to stabilise the amplifier in feedback configurations. This technique is called Miller compensation and functions in a similar manner to an op-amp integrator circuit. It is also known as 'dominant pole compensation' because it introduces a dominant pole (one which masks the effects of other poles) into the open loop frequency response. This pole can be as low as 10 Hz in a 741 amplifier and it introduces a -3 dB loss into the open loop response at this frequency. This internal compensation is provided to achieve unconditional stability of the amplifier in negative feedback configurations where the feedback network is non-reactive and the closed loop gain is unity or higher. Hence, the use of the operational amplifier is simplified because no external compensation is required for unity gain stability; amplifiers without this internal compensation may require external compensation or closed loop gains significantly higher than unity.

# Output bias circuitry

The green outlined section (based around Q16) is a voltage level shifter or rubber diode (i.e., a  $V_{BE}$  multiplier); a type of voltage source. In the circuit as shown, Q16 provides a constant voltage drop between its collector and emitter regardless of the current through the circuit. If the base current to the transistor is assumed to be zero, and the voltage between base and emitter (and across the 7.5 k $\Omega$  resistor) is 0.625 V (a typical value for a BJT in the active region), then the current through the 4.5 k $\Omega$  resistor will be the same as that through the 7.5 k $\Omega$ , and will produce a voltage of 0.375 V across it. This keeps the voltage across the transistor, and the two resistors at 0.625 + 0.375 = 1 V. This serves to bias the two output transistors slightly into conduction reducing crossover distortion. In some discrete component amplifiers this function is achieved with (usually two) silicon diodes.

# Output stage

The output stage (outlined in cyan) is a Class AB push-pull emitter follower (Q14, Q20) amplifier with the bias set by the  $V_{be}$  multiplier voltage source Q16 and its base resistors. This stage is effectively driven by the collectors of Q13 and Q19. Variations in the bias with temperature, or between parts with the same type number, are common so crossover distortion and quiescent current may be subject to significant variation. The output range of the amplifier is about one volt less than the supply voltage, owing in part to  $V_{be}$  of the output transistors Q14 and Q20.

The 25  $\Omega$  resistor in the output stage acts as a current sense to provide the output current-limiting function which limits the current in the emitter follower Q14 to about 25 mA for the 741. Current limiting for the negative output is done by sensing the voltage across Q19's emitter resistor and using this to reduce the drive into Q15's base. Later versions of this amplifier schematic may show a slightly different method of output current limiting. The output resistance is not zero, as it would be in an ideal op-amp, but with negative feedback it approaches zero at low frequencies.

Note: while the 741 was historically used in audio and other sensitive equipment, such use is now rare because of the improved noise performance of more modern op-amps. Apart from generating noticeable hiss, 741s and other older op-amps may have poor common-mode rejection ratios and so will often introduce cable-borne mains hum and other common-mode interference, such as switch 'clicks', into sensitive equipment.

The "741" has come to often mean a generic op-amp IC (such as uA741, LM 301, 558, LM 324, TBA221 - or a more modern replacement such as the TL071). The description of the 741 output stage is qualitatively similar for many other designs (that may have quite different input stages), except:

- Some devices (uA748, LM301, LM308) are not internally compensated (require an external capacitor from output to some point within the operational amplifier, if used in low closed-loop gain applications).

- Some modern devices have rail-to-rail output capability (output can be taken to positive or negative power supply rail within a few millivolts).

# See also

- Operational amplifier applications

- Differential amplifier

- Instrumentation amplifier

- Active filter

- Current-feedback operational amplifier

- Operational transconductance amplifier

- George A. Philbrick

- Analog computer

- Negative feedback amplifier

# Notes

- 1. ^ This definition hews to the convention of measuring op-amp parameters with respect to the zero voltage point in the circuit, which is usually half the total voltage between the amplifier's positive and negative power rails.

- 2. ^ Many older designs of operational amplifiers have offset null inputs to allow the offset to be manually adjusted away. Modern precision op-amps can have internal circuits that automatically cancel this offset using choppers or other circuits that measure the offset voltage periodically and subtract it from the input voltage.

- 3. ^ That the output cannot reach the power supply voltages is usually the result of limitations of the amplifier's output stage transistors. See "Output stage," below.

- 4. ^ The output of older op-amps can reach to within one or two volts of the supply rails. The output of newer so-called "rail to rail" op-amps can reach to within millivolts of the supply rails when providing low output currents.

# References

- 1. ^ MAXIM Application Note 1108: Understanding Single-Ended, Pseudo-Differential and Fully-Differential ADC Inputs (http://www.maxim-ic.com/appnotes.cfm/an\_pk/1108) Retrieved November 10, 2007

- 2. ^ Paul Horowitz and Winfield Hill, The Art of Electronics, Cambridge University Press, 1989, p 177.

- <sup>A</sup> Jung, Walter G. (2004). "Chapter 8: Op Amp History" (http://books.google.com/books?id=dunqt1rt4sAC). Op Amp Applications Handbook. Newnes. p. 777. ISBN 9780750678445. http://books.google.com /books?id=dunqt1rt4sAC. Retrieved 2008-11-15.

- <sup>A</sup> Jung, Walter G. (2004). "Chapter 8: Op Amp History" (http://books.google.com/books?id=dunqt1rt4sAC). Op Amp Applications Handbook. Newnes. p. 779. ISBN 9780750678445. http://books.google.com /books?id=dunqt1rt4sAC. Retrieved 2008-11-15.

- 5. ^ http://www.analog.com/library/analogDialogue/archives/39-05/Web\_ChH\_final.pdf

- 6. ^ A.P. Malvino, *Electronic Principles* (2<sup>nd</sup> Ed. 1979. ISBN 0-07-039867-4) p. 476.

- 7. ^ Electronic Circuits (Fifth edition) by Sedra/Smith

- 8. ^ D.F. Stout *Handbook of Operational Amplifier Circuit Design* (McGraw-Hill, 1976, ISBN 007061797X) pp. 1–11.

- 9. ^ The uA741 Operational Amplifier (http://ecow.engr.wisc.edu/cgi-bin/get/ece/342/schowalter/notes/chapter10 /theua741operationalamplifier.ppt)

# **External links**

- Introduction to op-amp circuit stages, second order filters, single op-amp bandpass filters, and a simple intercom (http://www.bowdenshobbycircuits.info/opamp.htm)

- Hyperphysics descriptions of common applications (http://hyperphysics.phy-astr.gsu.edu/hbase /electronic/opampvar.html)

- Single supply op-amp circuit collection (http://instruct1.cit.cornell.edu/courses/bionb440/datasheets /SingleSupply.pdf)

- Op-amp circuit collection (http://www.national.com/an/AN/AN-31.pdf)

- Another introduction (http://web.telia.com/~u85920178/begin/opamp00.htm)

- Op-Amp Handbook (http://www.engineering.uiowa.edu/~bme080/supplementary\_info /BBTI\_AppCkts.pdf)

- Opamps for everyone (http://focus.ti.com/lit/an/slod006b/slod006b.pdf) Downloadable book.

- MOS op amp design: A tutorial overview (http://www.ee.unb.ca/Courses/EE3122 /DFL/AdditionalMaterial/OpAmps/MOS\_OpAmpTutorial.pdf)

- High Speed OpAmp Techniques (http://cds.linear.com/docs/Application%20Note/an47fa.pdf) very practical and readable - with photos and real waveforms

- Op Amp Applications (http://www.analog.com/library/analogDialogue/archives/39-05 /op\_amp\_applications\_handbook.html) Downloadable book. Can also be bought

- Operational Amplifier Noise Prediction (All Op Amps) (http://www.intersil.com/data/an/an519.pdf) using spot noise

- Operational Amplifier Basics (http://www.williamson-labs.com/480\_opam.htm)

- History of the Op-amp (http://www.analog.com/library/analogDialogue/archives/39-05 /Web\_ChH\_final.pdf) from vacuum tubes to about 2002. Lots of detail, with schematics. IC part is somewhat ADI-centric.

- IC Op-Amps Through the Ages (http://www.calvin.edu/~pribeiro/courses/engr332/Handouts /ho18opamp.pdf)

- ECE 209: Operational amplifier basics (http://www.tedpavlic.com/teaching/osu/ece209/support /opamp\_basics.pdf) – Brief document explaining zero error by naive high-gain negative feedback. Gives single OpAmp example that generalizes typical configurations.

Retrieved from "http://en.wikipedia.org/wiki/Operational\_amplifier" Categories: Electronic amplifiers | Integrated circuits

- This page was last modified on 16 February 2010 at 17:42.

- Text is available under the Creative Commons Attribution-ShareAlike License; additional terms may apply. See Terms of Use for details.

Wikin adia® is a paristand trademark of the Wikimadia Foundation. Inc., a non-profit organization.

Wikipedia® is a registered trademark of the Wikimedia Foundation, Inc., a non-profit organization.

# **Operational amplifier applications**

From Wikipedia, the free encyclopedia

This article illustrates some typical **applications** of **operational amplifiers**. A simplified schematic notation is used, and the reader is reminded that many details such as device selection and power supply connections are not shown.

# Contents

- I Practical circuits

- 1.1 Power supply effects

- 2 Linear circuit applications

- 2.1 Comparator

- 2.2 Inverting amplifier

- 2.3 Non-inverting amplifier

- 2.4 Differential amplifier

- 2.4.1 Amplified difference

- 2.4.2 Difference amplifier

- 2.5 Voltage follower

- 2.6 Summing amplifier

- 2.7 Integrator

- 2.8 Differentiator

- 2.9 Instrumentation amplifier

- 2.10 Schmitt trigger

- 2.11 Relaxation oscillator

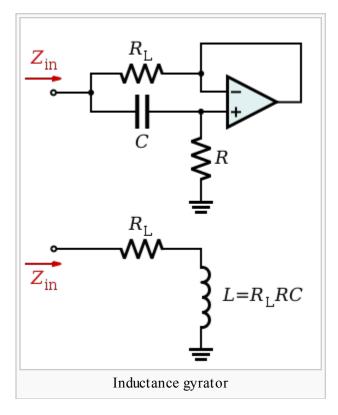

- 2.12 Inductance gyrator

- 2.13 Zero level detector

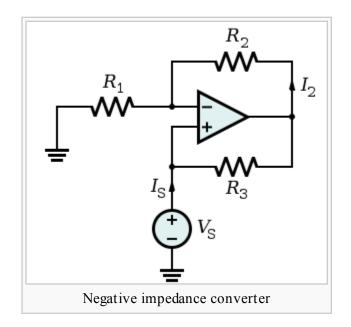

- 2.14 Negative impedance converter (NIC)

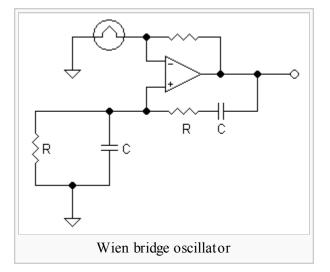

- 2.15 Wien bridge oscillator

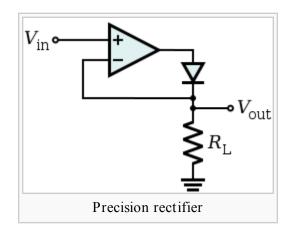

- 3 Non-linear configurations

- 3.1 Precision rectifier

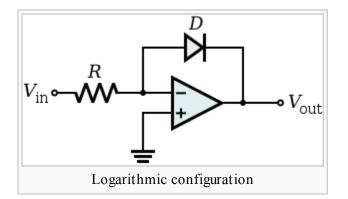

- 3.2 Logarithmic output

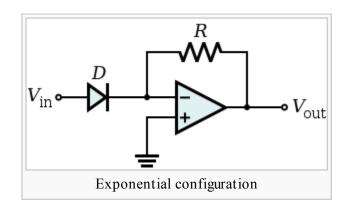

- 3.3 Exponential output

- 4 Other applications

- 5 See also

- 6 References

- 7 Further reading

- 8 External links

# **Practical circuits**

It is important to note that the equations shown below, pertaining to each type of circuit, assume that an ideal op amp is used. Those interested in construction of any of these circuits for practical use should consult a more detailed reference. See the External links and Further reading sections.

Resistors used in practical solid-state op-amp circuits are typically in the k $\Omega$  range. Resistors much greater than 1 M $\Omega$  cause excessive thermal noise and make the circuit operation susceptible to significant errors due to bias or leakage currents.

Practical operational amplifiers draw a small current from each of their inputs due to bias requirements and leakage. These currents flow through the resistances connected to the inputs and produce small voltage drops across those resistances. In AC signal applications this seldom matters. If high-precision DC operation is required, however, these voltage drops need to be considered. The design technique is to try to ensure that these voltage drops are equal for both inputs, and therefore cancel. If these voltage drops are equal and the common-mode rejection ratio of the operational amplifier is good, there will be considerable cancellation and improvement in DC accuracy.

If the input currents into the operational amplifier are equal, to reduce offset voltage the designer must ensure that the DC resistance looking out of each input is also matched. In general input currents differ, the difference being called the *input offset current*,  $I_{os}$ . Matched external input resistances  $R_{in}$  will still produce an input voltage error of  $R_{in} \cdot I_{os}$ . Most manufacturers provide a method for tuning the operational amplifier to balance the input currents (e.g., "offset null" or "balance" pins that can interact with an external voltage source attached to a potentiometer). Otherwise, a tunable external voltage can be added to one of the inputs in order to balance out the offset effect. In cases where a design calls for one input to be short-circuited to ground, that short circuit can be replaced with a variable resistance that can be tuned to mitigate the offset problem.

Note that many operational amplifiers that have MOSFET-based input stages have input leakage currents that will truly be negligible to most designs.

## **Power supply effects**

Although the power supplies are not shown in the operational amplifier designs below, they can be critical in operational amplifier design.

Power supply imperfections (e.g., power signal ripple, non-zero source impedance) may lead to noticeable deviations from ideal operational amplifier behavior. For example, operational amplifiers have a specified power supply rejection ratio that indicates how well the output can reject signals that appear on the power supply inputs. Power supply inputs are often noisy in large designs because the power supply is used by nearly every component in the design, and inductance effects prevent current from being instantaneously delivered to every component at once. As a consequence, when a component requires large injections of current (e.g., a digital component that is frequently switching from one state to another), nearby components can experience sagging at their connection to the power supply. This problem can be mitigated with copious use of bypass capacitors placed connected across each power supply pin and ground. When bursts of current are required by a component, the component can *bypass* the power supply by receiving the current directly from the nearby capacitor (which is then slowly charged by the power supply).

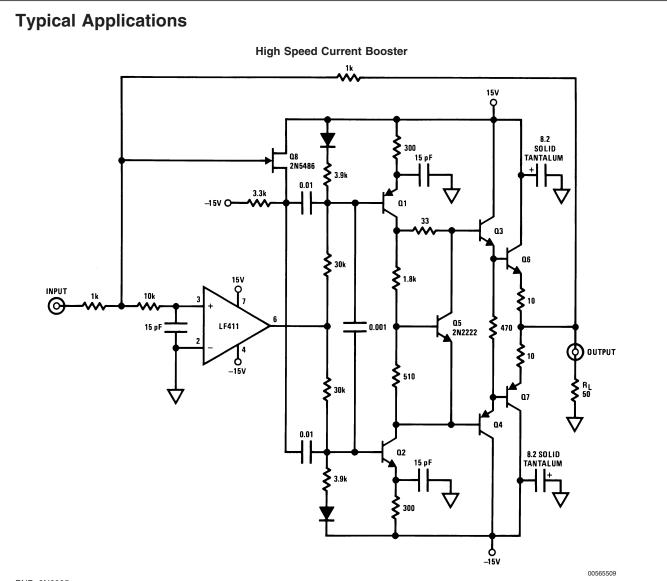

Additionally, current drawn into the operational amplifier from the power supply can be used as inputs to

external circuitry that augment the capabilities of the operational amplifier. For example, an operational amplifier may not be fit for a particular high-gain application because its output would be required to generate signals outside of the safe range generated by the amplifier. In this case, an external push–pull amplifier can be controlled by the current into and out of the operational amplifier. Thus, the operational amplifier may itself operate within its factory specified bounds while still allowing the negative feedback path to include a large output signal well outside of those bounds.<sup>[1]</sup>

# Linear circuit applications

## Comparator

#### Main article: Comparator

Compares two voltages and switches its output to indicate which voltage is larger.

$$\bullet V_{\text{out}} = \begin{cases} V_{\text{S+}} & V_1 > V_2 \\ V_{\text{S-}} & V_1 < V_2 \end{cases}$$

(where  $V_{\rm S}$  is the supply voltage and the opamp is powered by  $+ V_{\rm S}$  and  $- V_{\rm S}$ .)

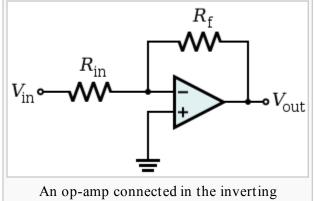

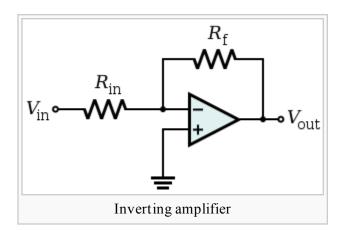

## **Inverting amplifier**

An inverting amplifier uses negative feedback to invert and amplify a voltage. The  $R_f$  resistor allows some of the output signal to be returned to the input. Since the output is 180° out of phase, this amount is effectively subtracted from the input, thereby reducing the input into the operational amplifier. This reduces the overall gain of the amplifier and is dubbed negative feedback.<sup>[2]</sup>

$$V_{\rm out} = -\frac{R_{\rm f}}{R_{\rm in}} V_{\rm in}$$

- $Z_{in} = R_{in}$  (because V is a virtual ground)

- A third resistor, of value  $R_{\rm f} || R_{\rm in} \triangleq R_{\rm f} R_{\rm in} / (R_{\rm f} + R_{\rm in})$ , added between the non-inverting input and ground, while not necessary, minimizes errors due to input bias currents.

#### [3]

The gain of the amplifier is determined by the ratio of Rfto Rin. That is:

$$A = -\frac{R_f}{R_{in}}$$

The presence of the negative sign is a convention indicating that the output is inverted. For example, if  $R_{\rm f}$  is 10,000  $\Omega$  and  $R_{\rm in}$  is 1,000  $\Omega$ , then the gain would be -10000 $\Omega$ /1000 $\Omega$ , which is -10. <sup>[4]</sup>

•V<sub>out</sub>

Comparator

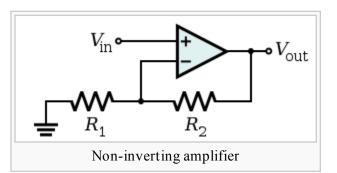

## Non-inverting amplifier

Amplifies a voltage (multiplies by a constant greater than 1)

$$V_{\rm out} = V_{\rm in} \left(1 + \frac{R_2}{R_1}\right)$$

• Input impedance  $Z_{\rm in} \approx \infty$

The input impedance is *at least* the impedance between non-inverting (+) and inverting (-) inputs, which is typically 1 MΩ to 10 TΩ,

plus the impedance of the path from the inverting (-) input to ground (i.e.,  $R_1$  in parallel with  $R_2$ ).

- Because negative feedback ensures that the non-inverting and inverting inputs match, the input impedance is actually **much higher**.

- Although this circuit has a large input impedance, it suffers from error of input bias current.

- The non-inverting (+) and inverting (-) inputs draw small leakage currents into the operational amplifier.

- These input currents generate voltages that act like unmodeled input offsets. These unmodeled effects can lead to noise on the output (e.g., offsets or drift).

- Assuming that the two leaking currents are **matched**, their effect can be mitigated by ensuring the DC impedance looking **out** of each input is the same.

- The voltage produced by each bias current is equal to the product of the bias current with the equivalent DC impedance looking out of each input. Making those impedances equal makes the offset voltage at each input equal, and so the non-zero bias currents will have no impact on the **difference** between the two inputs.

- A resistor of value

$$R_1 \| R_2 \triangleq \left( \frac{1}{R_1} + \frac{1}{R_2} \right)^{-1} = \frac{R_1 R_2}{R_1 + R_2},$$

which is the equivalent resistance of  $R_1$  in parallel with  $R_2$ , between the  $V_{in}$  source and the non-inverting (+) input will ensure the impedances looking **out** of each input will be matched.

- The matched bias currents will then generate matched offset voltages, and their effect will be hidden to the operational amplifier (which acts on the difference between its inputs) so long as the CMRR is good.

- Very often, the input currents are *not* matched.

- Most operational amplifiers provide some method of balancing the two input currents (e.g., by way of an external potentiometer).

- Alternatively, an external offset can be added to the operational amplifier input to nullify the effect.

• Another solution is to insert a variable resistor between the  $V_{in}$  source and the non-inverting

(+) input. The resistance can be tuned until the offset voltages at each input are matched.

Operational amplifiers with MOSFET-based input stages have input currents that are so small that they often can be neglected.

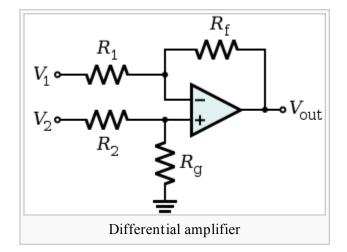

#### **Differential amplifier**

#### Main article: Differential amplifier

The circuit shown is used for finding the difference of two voltages each multiplied by some constant (determined by the resistors).

The name "differential amplifier" should not be confused with the "differentiator", also shown on this page.

$$V_{\text{out}} = \frac{(R_{\text{f}} + R_1) R_{\text{g}}}{(R_{\text{g}} + R_2) R_1} V_2 - \frac{R_{\text{f}}}{R_1} V_1$$

• Differential Z<sub>in</sub> (between the two input pins) =

$R_1 + R_2$  (Note: this is approximate)

For common-mode rejection, anything done to one input must be done to the other. The addition of a compensation capacitor in parallel with Rf, for instance, must be balanced by an equivalent capacitor in parallel with Rg.

The "instrumentation amplifier", which is also shown on this page, is another form of differential amplifier that also provides high input impedance.

#### **Amplified difference**

Whenever  $R_1 = R_2$  and  $R_f = R_g$ ,

$$V_{\text{out}} = A(V_2 - V_1) \text{ and } A \triangleq \frac{R_{\text{f}}}{R_1}$$

**Difference** amplifier

When  $R_1 = R_f$  and  $R_2 = R_g$ :

$$V_{\rm out} = V_2 - V_1$$

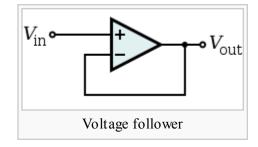

#### Voltage follower

Used as a buffer amplifier to eliminate loading effects (e.g., connecting a device with a high source impedance to a device with a low input impedance).

$V_{\text{out}} = V_{\text{in}}$  $Z_{\text{in}} = \infty$  (realistically, the differential input impedance of the op-amp itself, 1 M $\Omega$  to 1 T $\Omega$ )

Due to the strong (i.e., unity gain) feedback and certain non-ideal

characteristics of real operational amplifiers, this feedback system is prone to have poor stability margins. Consequently, the system may be unstable when connected to sufficiently capacitive loads. In these cases, a lag compensation network (e.g., connecting the load to the voltage follower through a resistor) can be used to restore stability. The manufacturer data sheet for the operational amplifier may provide guidance for the selection of components in external compensation networks. Alternatively, another operational amplifier can be chosen that has more appropriate internal compensation.

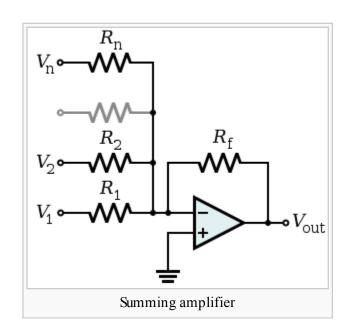

### Summing amplifier